Interconnection Networks Computer Architecture: A Quantitative Approach 4<sup>th</sup> Edition, Appendix E

> Timothy Mark Pinkston University of Southern California http://ceng.usc.edu/smart/slides/appendixE.html

José Duato Universidad Politécnica de Valencia http://www.gap.upv.es/slides/appendixE.html

...with major presentation contribution from José Flich, UPV (and Cell BE EIB slides by Tom Ainsworth, USC)

# Outline

- E.1 Introduction (Lecture 1)

- E.2 Interconnecting Two Devices (Lecture 1)

- E.3 Interconnecting Many Devices (Lecture 2)

- E.4 Network Topology (Lecture 2)

- E.5 Network Routing, Arbitration, and Switching (Lecture 3)

- E.6 Switch Microarchitecture (Lecture 4)

- E.7 Practical Issues for Commercial Interconnection Networks (Lec 4)

- E.8 Examples of Interconnection Networks (Lecture 5)

- E.9 Internetworking (skipped)

- E.10 Crosscutting Issues for Interconnection Networks (skipped)

- E.11 Fallacies and Pitfalls (Lecture 5)

- E.12 Concluding Remarks and References (Lecture 5)

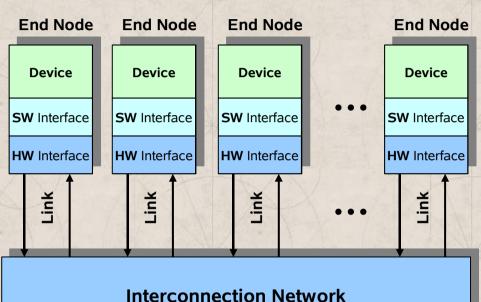

How to connect individual devices together into a community

of communicating devices?

- Device (definition):

- Component within a computer

- Single computer

- System of computers

- Types of elements:

- end nodes (device + interface)

- links

- interconnection network

- Internetworking: interconnection of multiple networks

- Interconnection networks should be designed to transfer the maximum amount of information within the least amount of time (and cost, power constraints) so as not to bottleneck the system

### Reasons to devote attention to interconnection networks

- They provide external connectivity from system to outside world

- Also, connectivity within a single computer system at many levels

- I/O units, boards, chips, modules and blocks inside chips

- Trends: high demand on communication bandwidth

- increased computing power and storage capacity

- switched networks are replacing buses

- Computer architects <u>must understand interconnect problems and</u> <u>solutions</u> in order to more effectively design and evaluate systems

### **Application domains**

- Networks implemented within processor chips and systems

- Networks implemented across systems

### Goal

- To provide an overview of network problems and solutions

- Examine a few case studies and examples

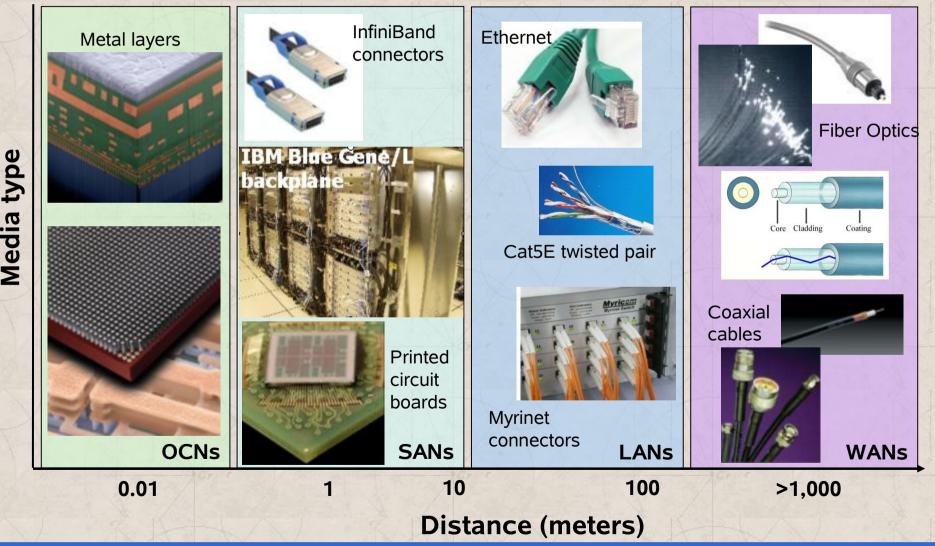

#### **Interconnection Network Domains**

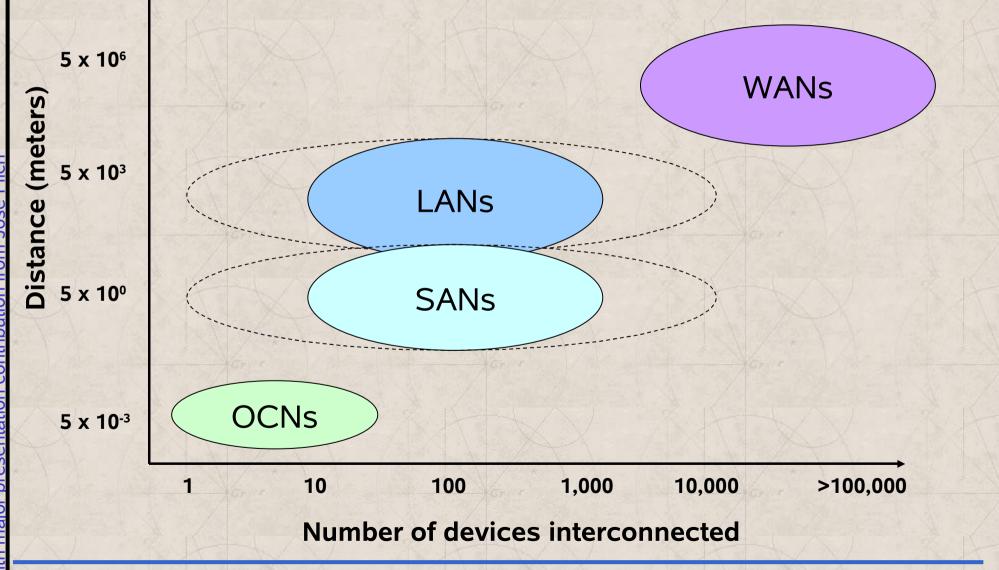

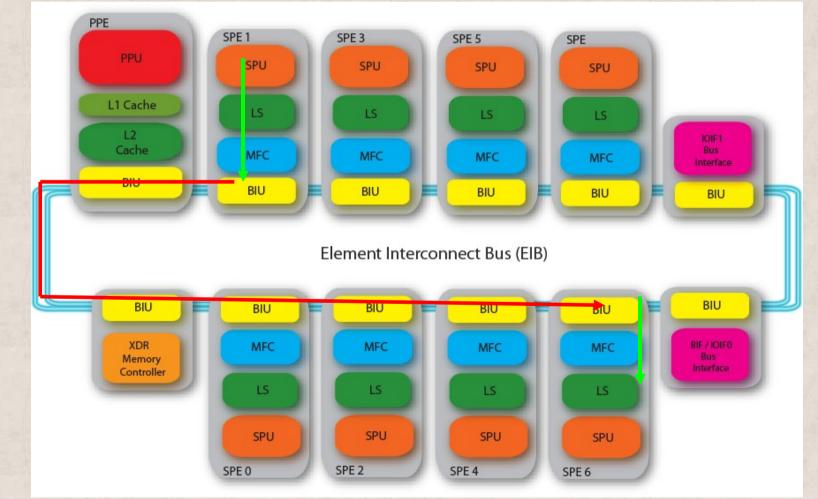

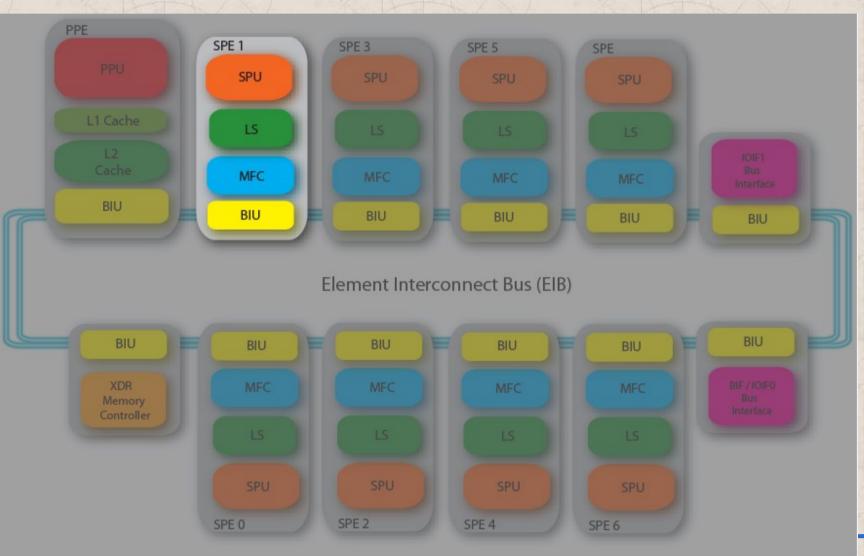

Interconnection networks can be grouped into *four major networking domains*, depending on the *number* and *proximity* of devices to be interconnected: *OCNs, SANs, LANs,* and *WANs*

- On-chip networks (OCNs), a.k.a., network-on-chip (NoC)

- Interconnect microarchitecture functional units, register files, caches, compute tiles, processor and IP cores

- Chip or multichip modules

- Tens (in future, possibly 100s) of devices interconnected

- Maximum interconnect distance on the order of centimeters

- Examples (custom designed)

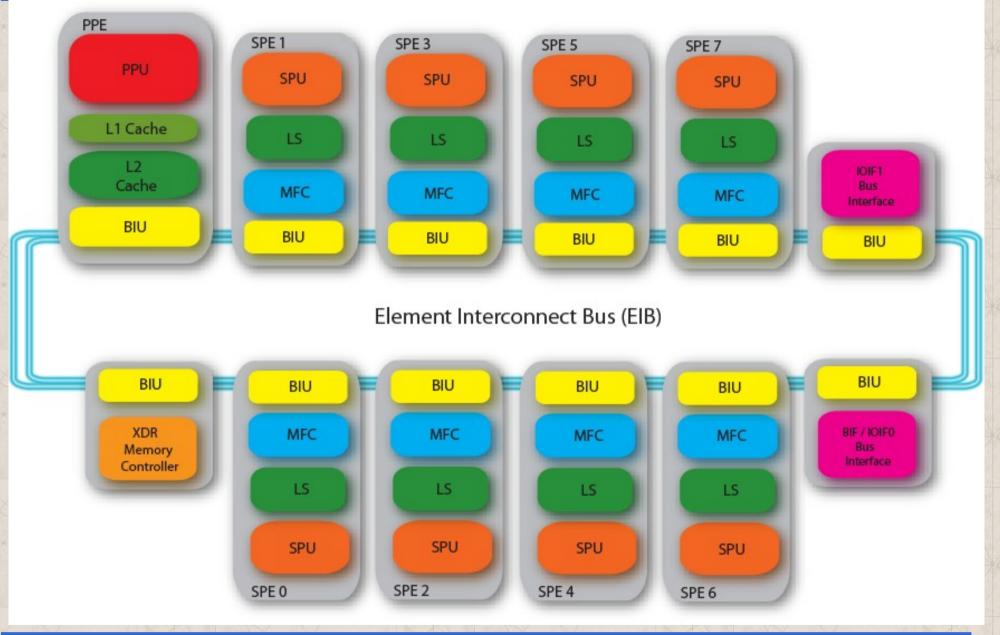

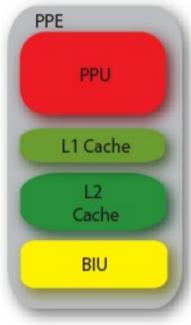

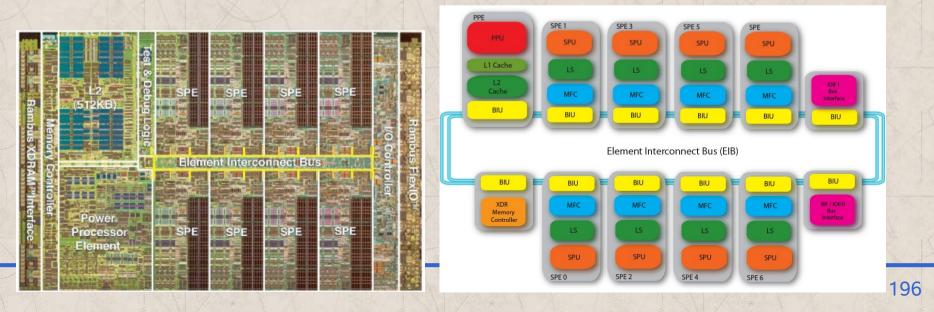

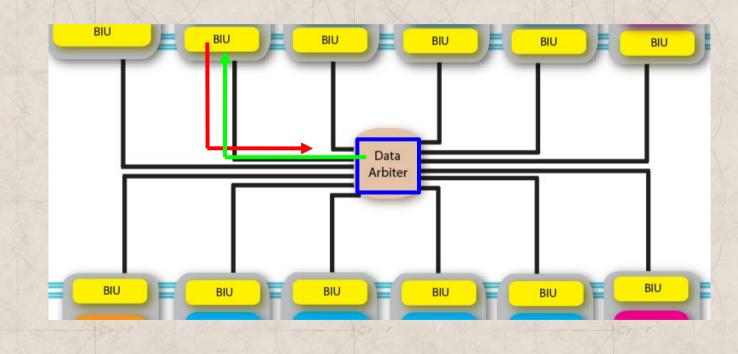

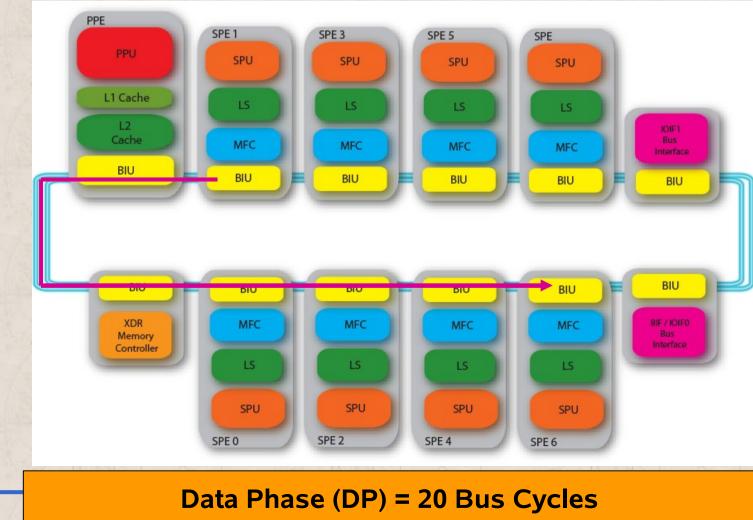

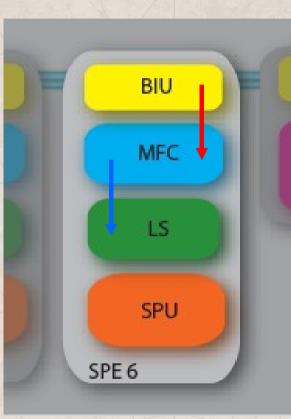

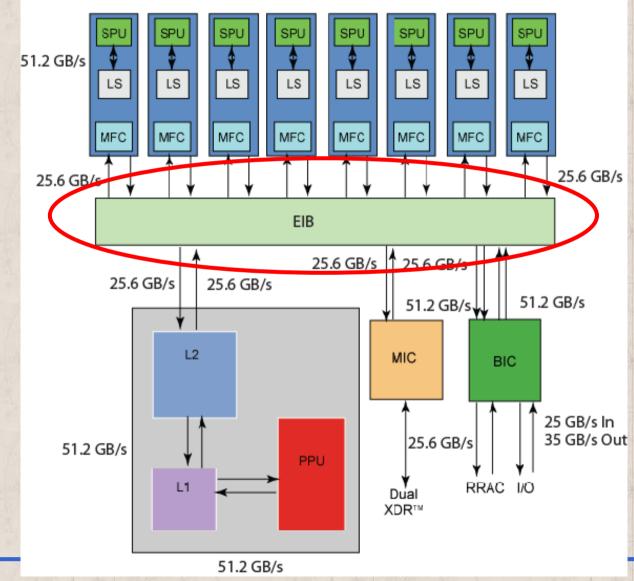

- Element Interconnect Bus (Cell Broadband Engine processor chip)

- » 2,400 Gbps (3.2 Ghz processor clock), 12 elements on the chip

- Examples (proprietary designs)

- CoreConnect (IBM), AMBA (ARM), Smart Interconnect (Sonic)

#### **Interconnection Network Domains**

- System/storage area networks (SANs)

- Multiprocessor and multicomputer systems

- Interprocessor and processor-memory interconnections

- Server and data center environments

- > Storage and I/O components

- Hundreds to thousands of devices interconnected

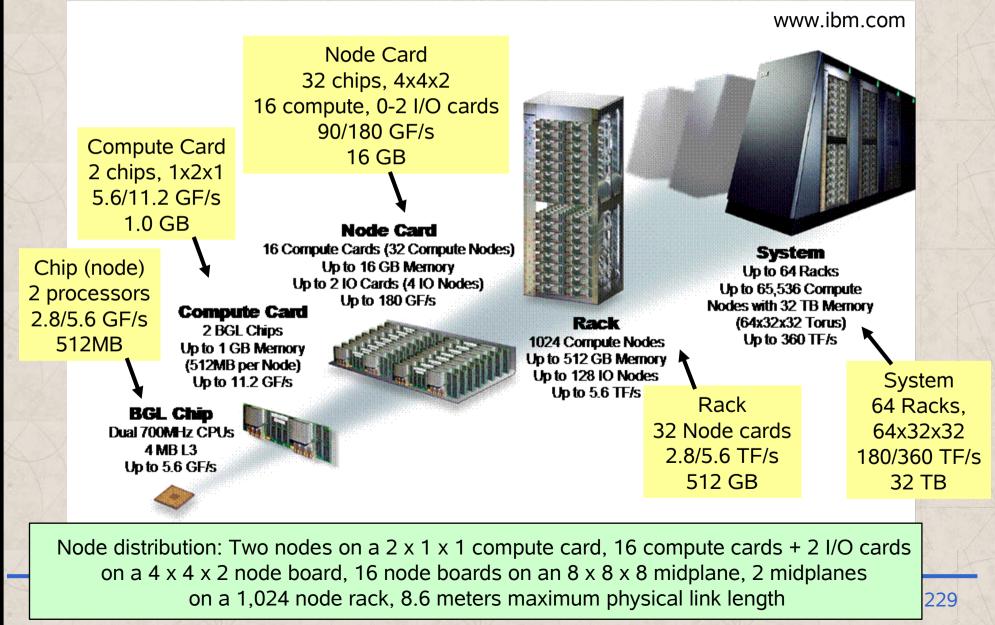

- IBM Blue Gene/L supercomputer (64K nodes, each with 2 processors)

- Maximum interconnect distance typically on the order of tens of meters, but some with as high as a few hundred meters

- InfiniBand: 120 Gbps over a distance of 300 m

- Examples (standards and proprietary)

- > InfiniBand, Myrinet, Quadrics, Advanced Switching Interconnect

### **Interconnection Network Domains**

- Local area networks (LANs)

- Interconnect autonomous computer systems

- Machine room or throughout a building or campus

- Hundreds of devices interconnected (1,000s with bridging)

- Maximum interconnect distance on the order of few kilometers, but some with distance spans of a few tens of kilometers

- Hundred devices (thousands with bridging)

- Example (most popular): Ethernet, with 10 Gbps over 40Km

- Wide area networks (WANs)

- Interconnect systems distributed across the globe

- Internetworking support is required

- Many millions of devices interconnected

- Maximum interconnect distance of many thousands of kilometers

- Example: ATM

#### Interconnection Network Domains

Timothy Mark Pinkston and José Duato osé Flich contribution from Interconnection Networks: © sentation bre major with

#### Organization

- Top-down Approach

- We unveil concepts and complexities involved in designing interconnection networks by first viewing the network as an ideal "black box" and then systematically removing various layers of the black box, exposing non-ideal behavior and complexities.

- We first consider interconnecting only two devices (E.2)

- We then consider interconnecting many devices (E.3)

- Other layers of the black box are peeled away, exposing the network topology, routing, arbitration, and switching (E.4, E.5)

- We then zoom in on the switch microarchitecture (E.6)

- Next, we consider Practical Issues for Interconnection Networks (E.7)

- Finally, we look at some examples: OCNs and SANs (E.8)

- Internetworking (E.9) (skipped)

- Additional Crosscutting Issues (E.10) (skipped)

- Fallacies and Pitfalls (E.11)

- Concluding Remarks (E.12) and References

# Outline

- E.1 Introduction (Lecture 1)

- E.2 Interconnecting Two Devices (Lecture 1)

- An Ideal Network

- Network Interface Functions

- Communication Protocol

- Basic Network Structure and Functions

- Characterizing Performance: Latency & Effective Bandwidth

- Basic Network Characteristics in Commercial Machines

- E.3 Interconnecting Many Devices (Lecture 2)

- E.4 Network Topology (Lecture 2)

- E.5 Network Routing, Arbitration, and Switching (Lecture 3)

- E.6 Switch Microarchitecture (Lecture 4)

- E.7 Practical Issues for Commercial Interconnection Networks (Lecture 4)

- E.8 Examples of Interconnection Networks (Lecture 5)

- E.9 Internetworking (skipped)

- E.10 Crosscutting Issues for Interconnection Networks (skipped)

- E.11 Fallacies and Pitfalls (Lecture 5)

- E.12 Concluding Remarks and References (Lecture 5)

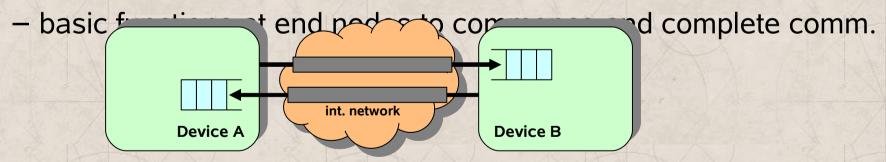

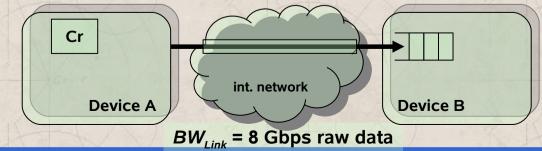

#### An Ideal Network

- Two end node devices (A and B)

- Device A (or B) may read an address in device B (or A)

- Interconnection network behaves as *dedicated links* between A, B

- Unidirectional wires each way dedicated to each device

- Receiving buffers used for staging the transfers at the end nodes

- Communication protocol: request, reply

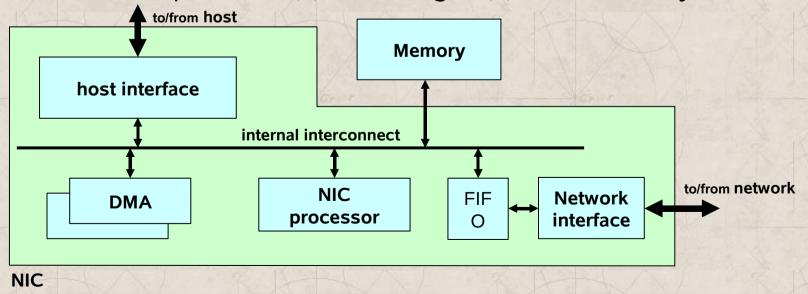

#### **Network Interface Functions**

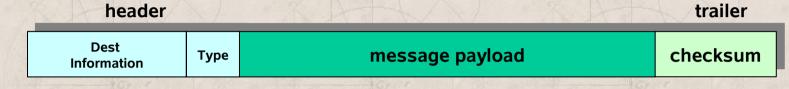

• A message is the unit of information: header, payload, trailer

- Interfacing to the network (hardware)

- Communication device itself (OCNs and some SANs)

- Additional network interface card or NIC (SANs, LANs, WANs)

- > Embedded processor(s), DMA engine(s), RAM memory

#### **Network Interface Functions**

- Interfacing to the network (software, firmware)

- Translate requests and replies into messages

- Tight integration with operating system (OS)

- > Process isolation, protection mechanisms, etc.

- Port (binds sender process with intended receiver process)

- Packetization

- > Maximum transfer unit (MTU) used for dimensioning resources

- > Messages larger than MTU divided into *packets* with *message id*

- Packet reordering at destination (for message reassembly) is done using sequence numbers

| header       |           |           | 100    |                                          | trailer  |

|--------------|-----------|-----------|--------|------------------------------------------|----------|

| Dest<br>Info | Msg<br>ID | Seq.<br># | Туре   | packet payload                           | checksum |

| The second   |           | G         | 01 = 1 |                                          |          |

|              |           |           |        | request acknowledge<br>reply acknowledge |          |

- Defines the sequence of steps followed by sender and receiver

- Implemented by a combination of software and hardware

- Hardware timers, CRC, packet processing, TLBs, ...

- TCP off-load engines for LANs, WANs

- OS-bypassing (zero-copy protocols)

- > Direct allocation of buffers at the network interface memory

- Applications directly read/write from/to these buffers

- > Memory-to-memory copies avoided

- Protection guaranteed by OS

#### **Communication Protocol**

>

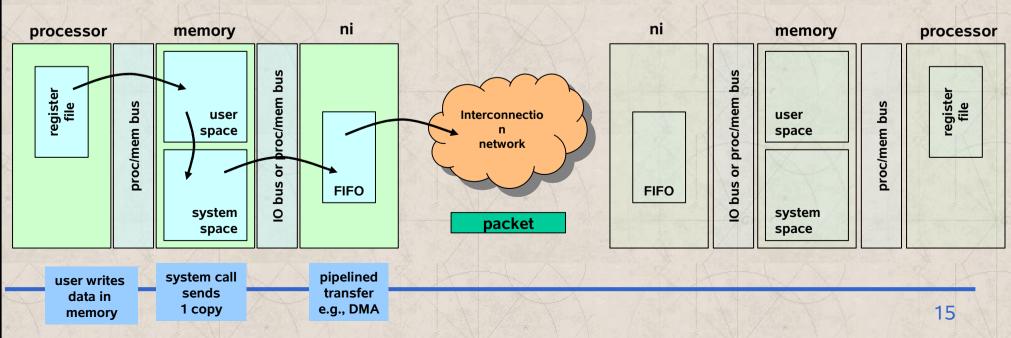

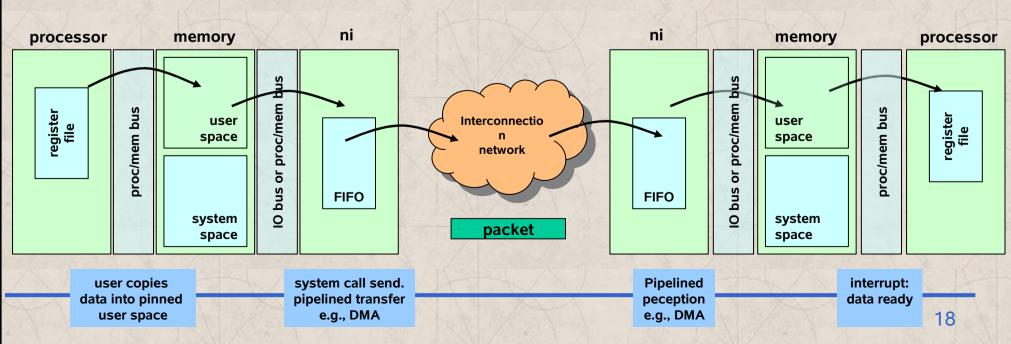

- Typical steps followed by the sender:

- 1. System call by application

- > Copies the data into OS and/or network interface memory

- Packetizes the message (if needed)

- Prepares headers and trailers of packets

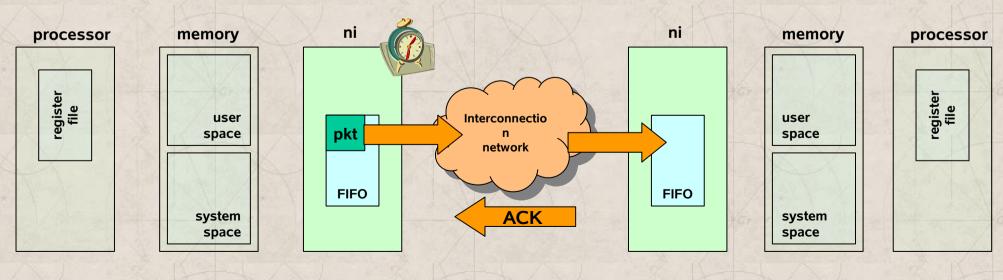

- 2. Checksum is computed and added to header/trailer

- 3. Timer is started and the network interface sends the packets

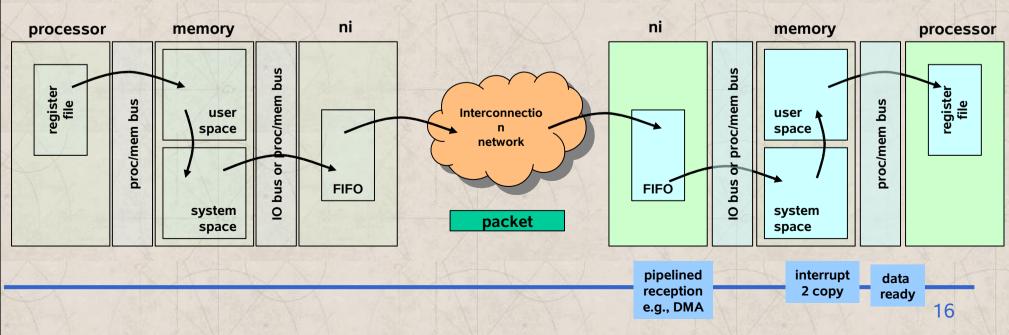

- Typical steps followed by the *receiver*:

- 1. NI allocates received packets into its memory or OS memory

- 2. Checksum is computed and compared for each packet

- If checksum matches, NI sends back an ACK packet

- 3. Once all packets are correctly received

- > The message is reassembled and copied to user's address space

- > The corresponding application is signalled (via polling or interrupt)

- Additional steps at the sender side:

- ACK received: the copy is released and timer is cancelled

- Timer expires before receiving an ACK: packet is resent and the timer is started

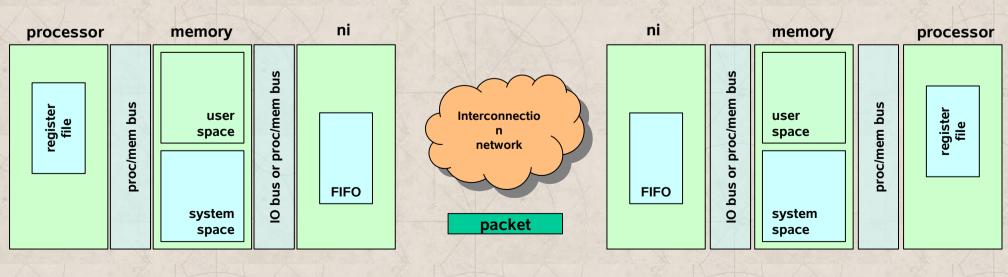

- OS-bypassing (zero-copy or user-level protocols)

- Direct allocation for DMA transfer to/from memory/NI buffers

- Application directly reads/writes from/to these locations

- Memory-to-memory copies are avoided

- Protection is guaranteed by OS

- OS-bypassing (zero-copy or user-level protocols)

- Direct allocation for DMA transfer to/from memory/NI buffers

- Application directly reads/writes from/to these locations

- Memory-to-memory copies are avoided

- Protection is guaranteed by OS

- Is it possible to take out register to memory/buffer copy as well?

- OS-bypassing (zero-copy or user-level protocols)

- Direct allocation of system or network interface memory/buffers

- Application directly reads/writes from/to these locations

- Memory-to-memory copies are avoided

- Protection is guaranteed by OS

- Is it possible to take out register to memory/buffer copy as well?

- NI buffer is associated with (or replaced by) register mapping

### Raw's 5-tuple Model (Taylor, et al. TPDS 2004):

- Defines a figure of merit for operation-operand matching

- End-to-end model: follows timing from sender to receiver

- 5-tuple: <SO, SL, NHL, RL, RO>

- SO: Send Occupancy

- SL: Send Latency

- NHL: Network Hop Latency

- RL: Receive Latency

- RO: Receive Occupancy

- Conventional distr. SM MP:

- Raw / msg passing:

- Raw / scalar:

- ILDP:

- Grid:

- Superscalar:

<10, 30, 5, 30, 40> < 3, 2, 1, 1, 7> < 0, 1, 1, 1, 0> <0, n, 0, 1, 0>, (n = 0, 2) <0, 0, n/8, 0, 0>, (n = 0..8) < 0, 0, 0, 0, 0>

"Scalar Operand Networks," M. B. Taylor, W. Lee, S. P. Amarasinghe, and A. Agarwal, *IEEE Trans. on Parallel*<sub>21</sub> and Distributed Systems, Vol. 16, No. 2, pp. 145–162, February, 2005.

### **Basic Network Structure and Functions**

- Media and Form Factor

- largely depends on distance and signaling rate

- up to centimeters (OCNs)

- > middle and upper copper metal layers at multi-gigabit rates

- up to meters (SANs)

- several layers of copper traces or tracks imprinted on circuit boards, midplanes, and backplanes at gigabit rates (differential-pair signaling); Cat 5 unshielded twisted-pair copper wiring

- 100 meter distances (LANs)

- Cat 5E unshielded twisted-pair copper wiring at 0.25 Gbps

- Kilometer distances and beyond (WANs)

- Coaxial copper cables at 10 Mbps

- Optical media allows faster transmission speeds

- » Multimode and WDM techniques allow 100s to 1,000s Mbps

#### **Basic Network Structure and Functions**

Media and Form Factor •

Timothy Mark Pinkston and José Duato José Flich contribution from nterconnection Networks: © sentation pre major with

Media

### **Basic Network Structure and Functions**

- Packet Transport

- Hardware circuitry needed to drive network links

- Encoding at the sender and decoding at the receiver

- > Multiple voltage levels, redundancy, data & control rotation (4b/5b)

- Encoding—along with packet headers and trailers—adds some overhead, which reduces link efficiency

- Physical layer abstraction:

- > viewed as a long linear pipeline without staging

- > signals propagate as waves through the transmission medium

### **Basic Network Structure and Functions**

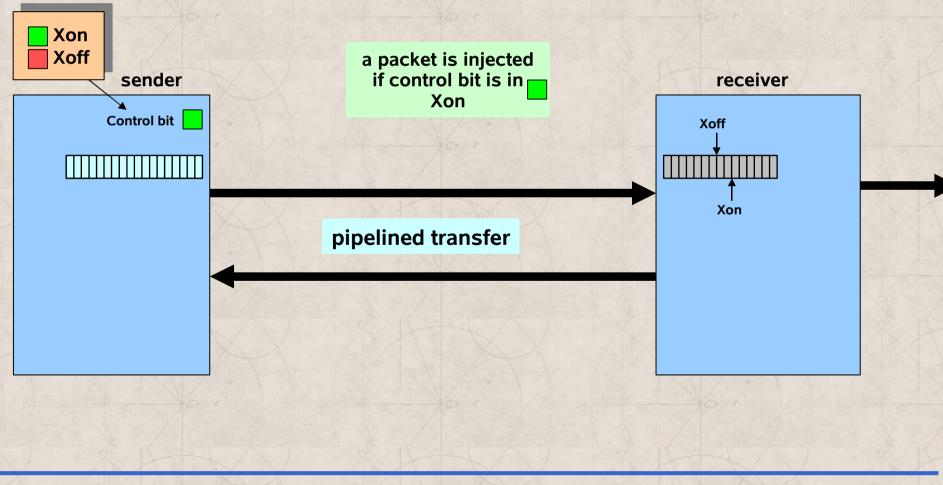

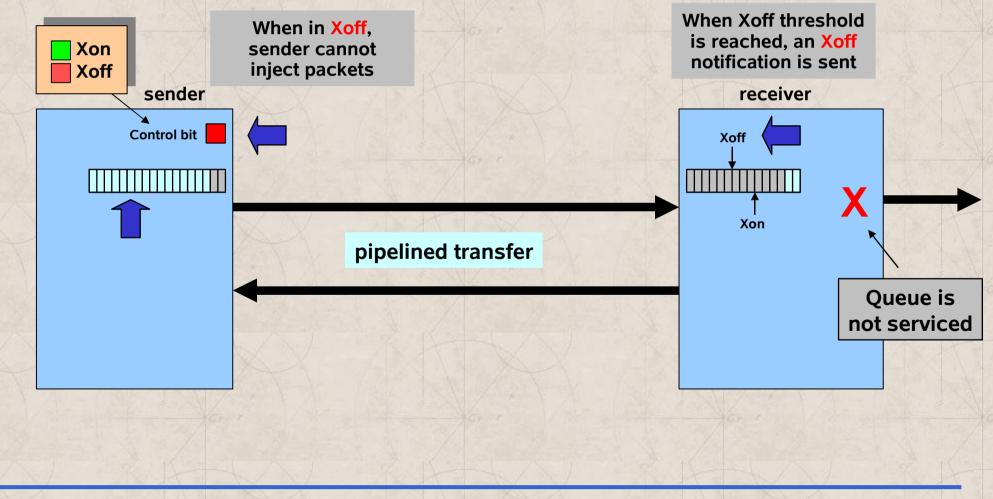

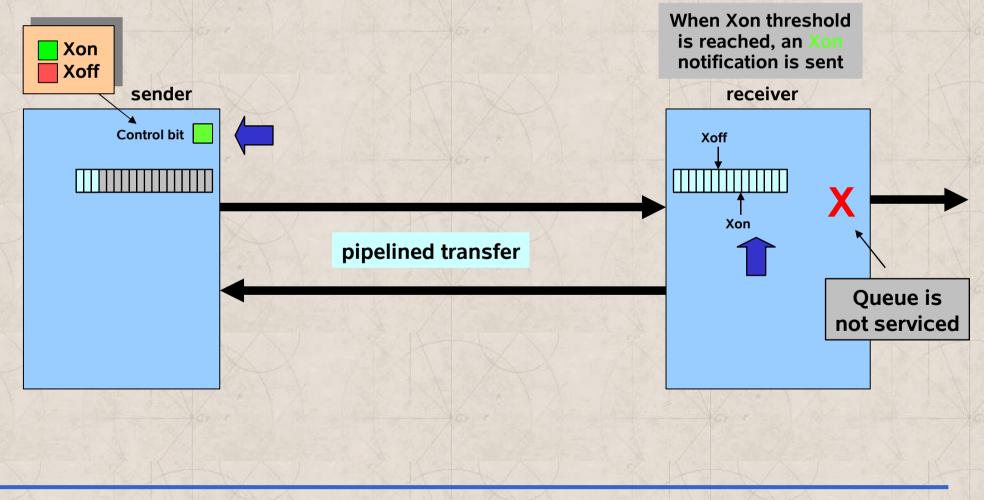

- Reliable delivery of packets: lossy versus lossless networks

- Must prevent the sender from sending packets at a faster rate than can be received and processed by the receiver

- Lossy networks

- > Packets are dropped (discarded) at receiver when buffers fill up

- Sender is notified to retransmit packets (via time-out or NACK)

- Lossless networks (flow controlled)

- > Before buffers fill up, sender is notified to stop packet injection

- » Xon/Xoff (Stop & Go) flow control

- » Credit-based flow control (token or batched modes)

- Implications of network type (lossless vs. lossy)

- > Constrains the solutions for packet routing, congestion, & deadlock

- Affects network performance

- > The interconnection network domain dictates which is used

- » OCN, SAN: typically lossless; LAN, WAN: typically lossy

#### **Basic Network Structure and Functions**

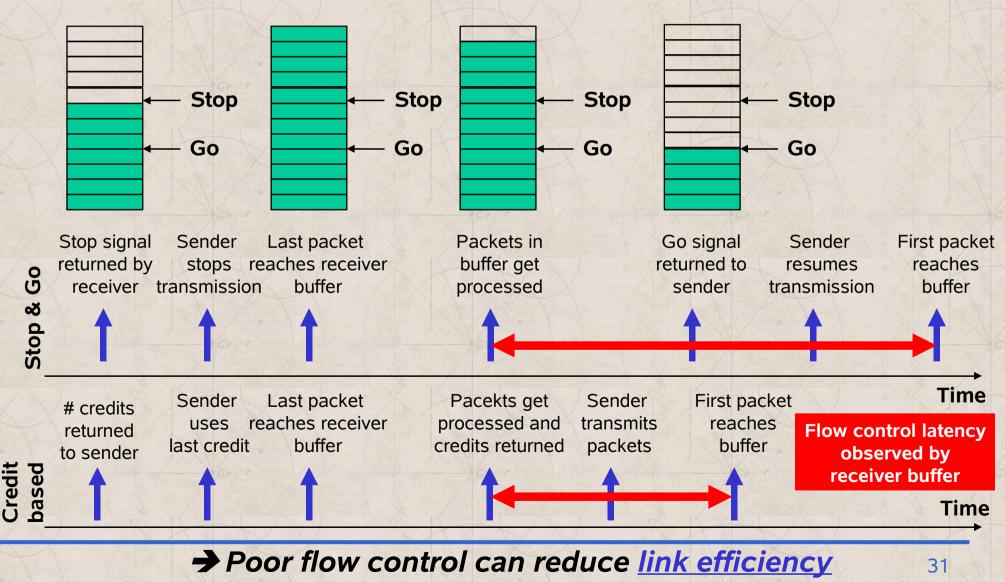

Xon/Xoff flow control

#### **Basic Network Structure and Functions**

Xon/Xoff flow control

#### **Basic Network Structure and Functions**

Xon/Xoff flow control

#### **Basic Network Structure and Functions**

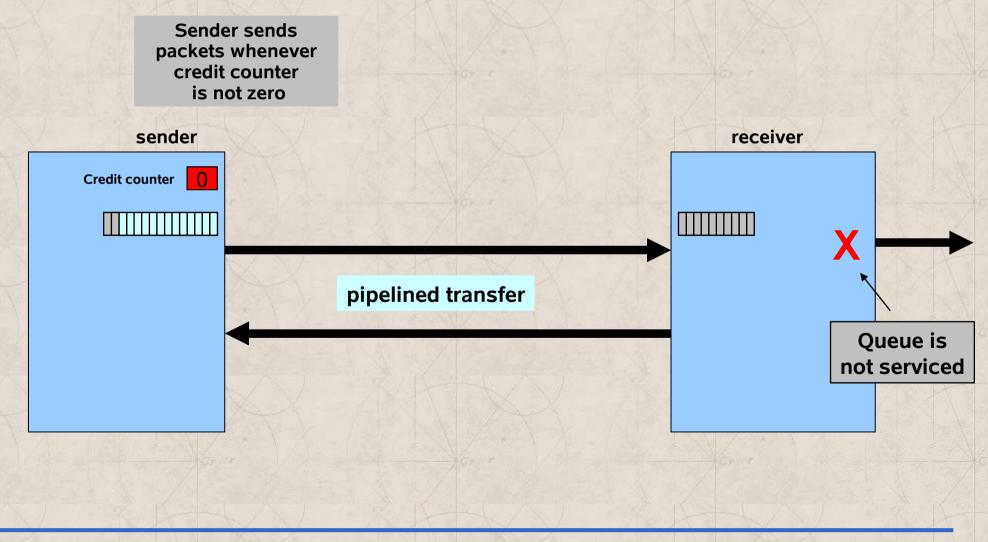

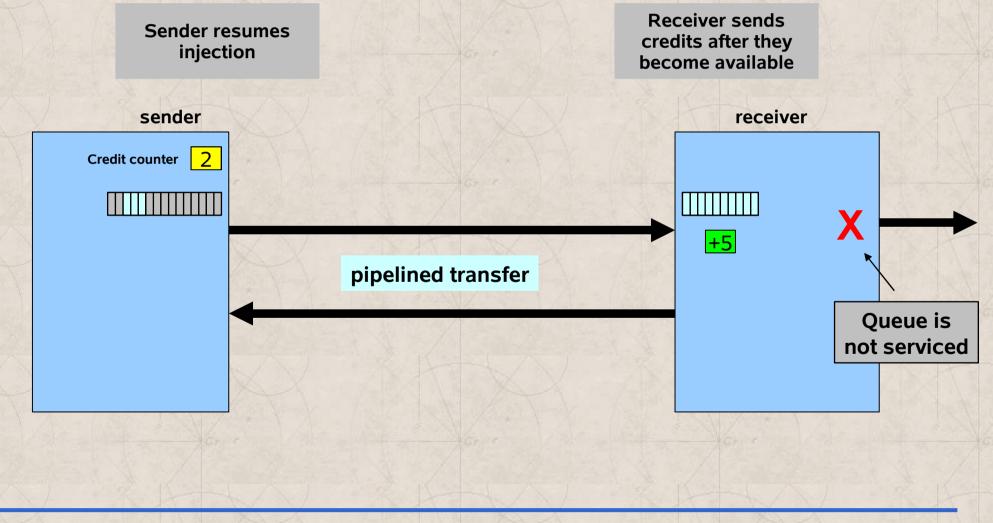

Credit-based flow control

#### **Basic Network Structure and Functions**

Credit-based flow control

#### **Basic Network Structure and Functions**

Comparison of Xon/Xoff vs credit-based flow control

#### **Basic Network Structure and Functions**

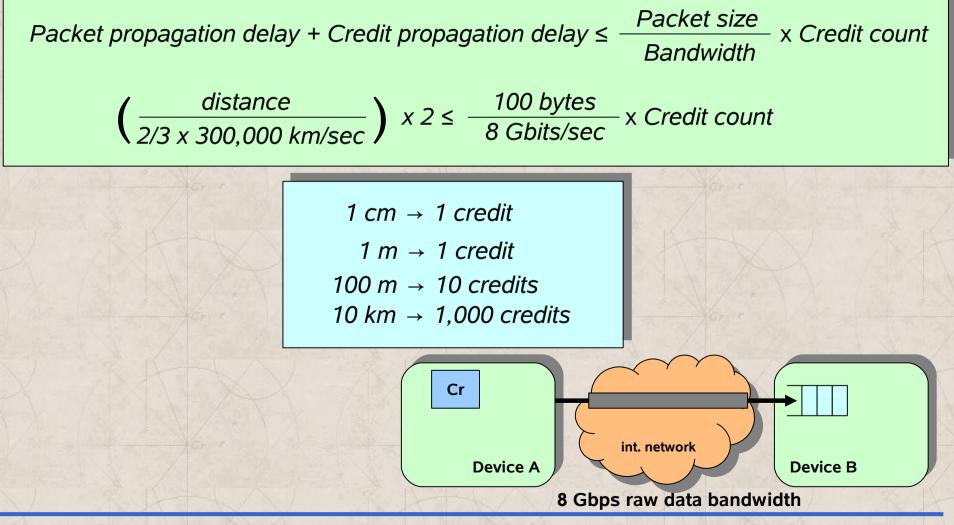

- Example: comparison of flow control techniques

- Calculate the minimum amount of credits and buffer space for interconnect distances of 1 cm, 1 m, 100 m, and 10 km

- Assume a dedicated-link network with

- > 8 Gbps (raw) data bandwidth per link (each direction)

- Credit-based flow control

- Device A continuously sends 100-byte packets (header included)

- Consider only the link propagation delay (no other delays or overheads)

**Basic Network Structure and Functions**

• Example: comparison of flow control techniques

#### **Basic Network Structure and Functions**

- *Error handling*: must detect and recover from transport errors

- Checksum added to packets

- Timer and ACK per packet sent

- Additional basic functionality needed by the protocol

- Resolve duplicates among packets

- Byte ordering (Little Endian or Big Endian)

- Pipelining across operations

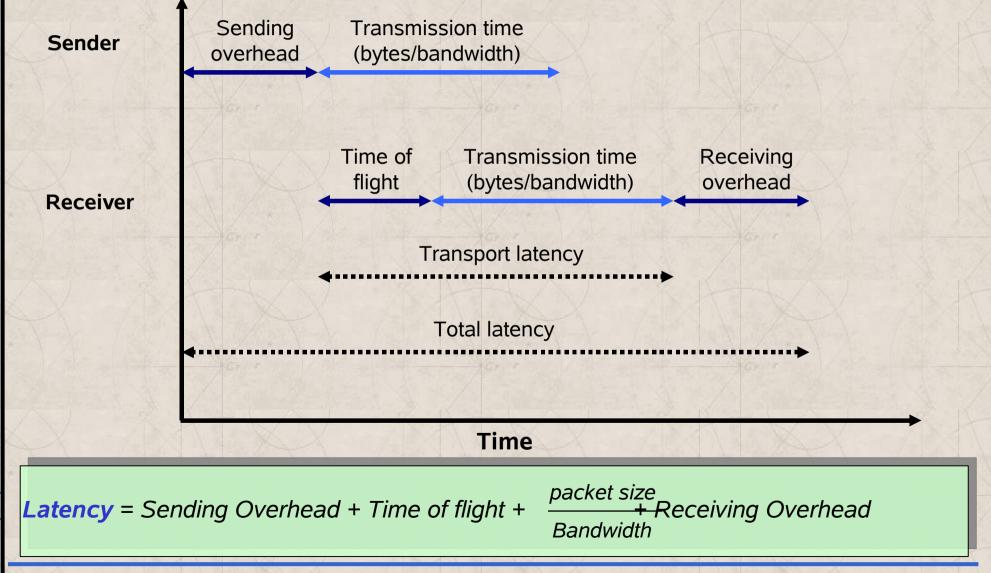

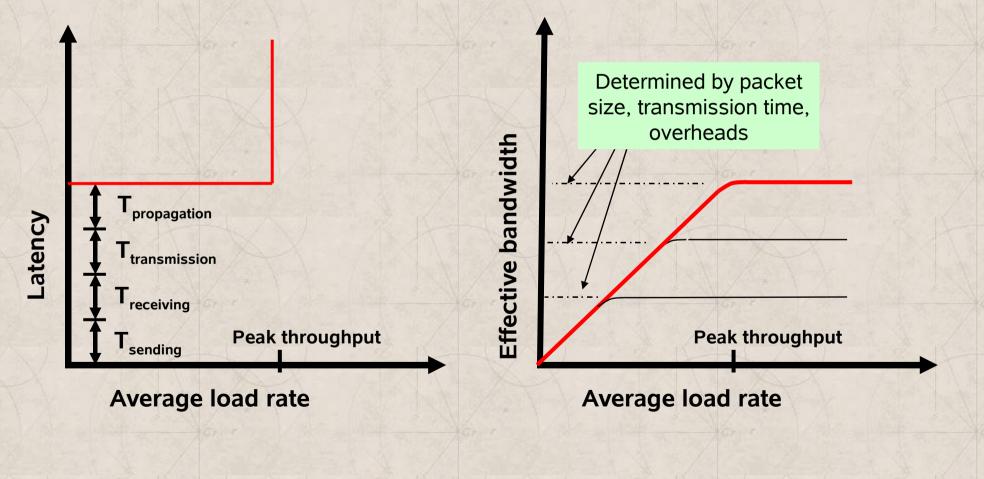

### Characterizing Performance: Latency & Effective Bandwidth Terms and Definitions:

- Bandwidth:

- Maximum rate at which information can be transferred (including packet header, payload and trailer)

- Unit: bits per second (bps) or bytes per second (Bps)

- Aggregate bandwidth: Total data bandwidth supplied by network

- *Effective bandwidth* (*throughput*): fraction of aggregate bandwidth that gets delivered to the application

- *Time of flight*: Time for first bit of a packet to arrive at the receiver

- Includes the time for a packet to pass through the network, not including the transmission time (defined next)

- Picoseconds (OCNs), nanoseconds (SANs), microseconds (LANs), milliseconds (WANs)

### Characterizing Performance: Latency & Effective Bandwidth

- Transmission time:

- The time for a packet to pass through the network, not including the time of flight

- > Equal to the packet size divided by the data bandwidth of the link

#### • Transport latency:

- > Sum of the time of flight and the transmission time

- > Measures the time that a packet spends in the network

- Sending overhead (latency):

- > Time to prepare a packet for injection, including hardware/software

- > A constant term (packet size) plus a variable term (buffer copies)

- Receiving overhead (latency):

- > Time to process an incoming packet at the end node

- > A constant term plus a variable term

- > Includes cost of interrupt, packet reorder and message reassembly

- Example (latency): calculate the total packet latency for interconnect distances of 0.5 cm, 5 m, 5,000 m, and 5,000 km

- Assume a dedicated-link network with

- > 8 Gbps (raw) data bandwidth per link, credit-based flow control

- Device A sends 100-byte packets (header included)

- Overheads

- > Sending overhead: x + 0.05 ns/byte

- > Receiving overhead: 4/3(x) + 0.05 ns/byte

- > x is 0  $\mu$ s for OCN, 0.3  $\mu$ s for SAN, 3  $\mu$ s for LAN, 30  $\mu$ s for WAN

- Assume time of flight consists only of link propagation delay (no other sources of delay)

#### **Characterizing Performance: Latency & Effective Bandwidth**

• Example (latency):

Latency = Sending overhead + Time of flight +  $\frac{F}{T}$

+ <u>Packet size</u> Bandwidth

- + Receiving overhead

Latency<sub>OCN</sub> = 5 ns + 0.025 ns + 100 ns + 5 ns = 110.025 ns Latency<sub>SAN</sub> = 0.305  $\mu$ s + 0.025 ns + 0.1  $\mu$ s + 0.405  $\mu$ s = 0.835  $\mu$ s Latency<sub>LAN</sub> = 3.005  $\mu$ s + 25  $\mu$ s + 0.1  $\mu$ s + 4.005  $\mu$ s = 32.11  $\mu$ s Latency<sub>WAN</sub> = 20.05  $\mu$ s + 25  $\mu$ s + 0.1  $\mu$ s + 40.05  $\mu$ s = 25.07 ms

#### Characterizing Performance: Latency & Effective Bandwidth

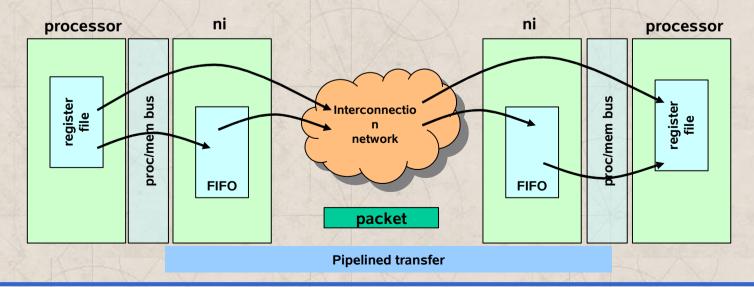

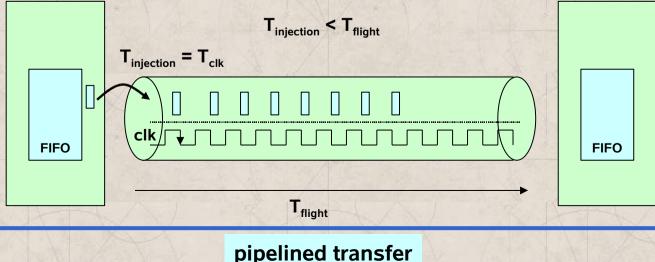

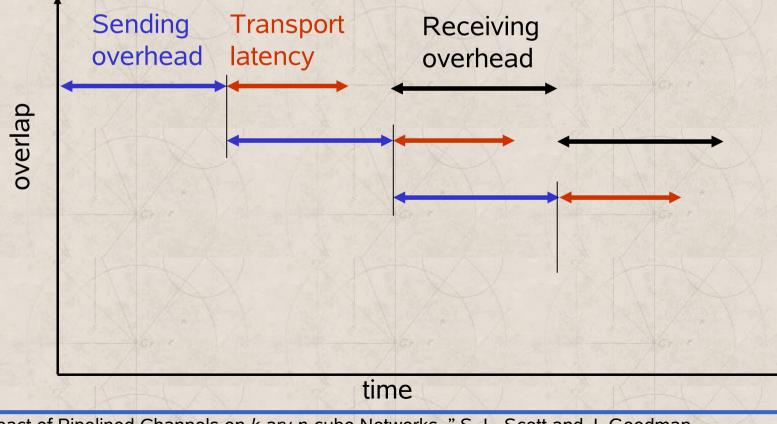

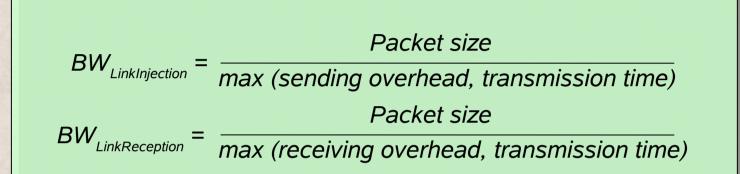

- Effective bandwidth with link pipelining

- Pipeline the flight and transmission of packets over the links

- Overlap the sending overhead with the transport latency and receiving overhead of prior packets

"The Impact of Pipelined Channels on *k*-ary *n*-cube Networks," S. L. Scott and J. Goodman, *IEEE Trans. on Parallel and Distributed Systems*, Vol. 5, No. 1, pp. 1–16, January, 1994.

#### Characterizing Performance: Latency & Effective Bandwidth

- Effective bandwidth with link pipelining

- Pipeline the flight and transmission of packets over the links

- Overlap the sending overhead with the transport latency and receiving overhead of prior packets

Eff. bandwidth = min  $(2xBW_{LinkInjection}, 2xBW_{LinkReception}) = \frac{2 x Packet size}{max (overhead, transmission time)}$ (only two devices) overhead = max (sending overhead, receiving overhead)

#### **Characterizing Performance: Latency & Effective Bandwidth**

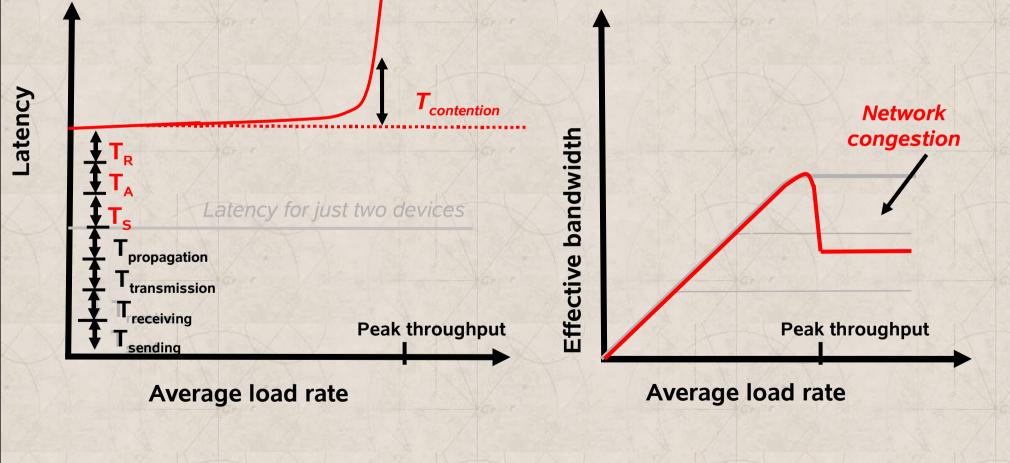

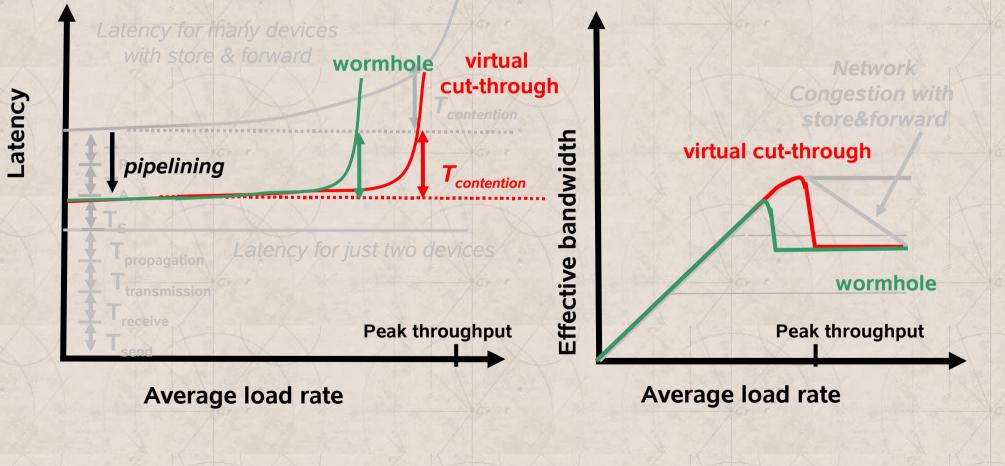

Characteristic performance plots: latency vs. average load rate; throughput (effective bandwidth) vs. average load rate

José Duato **Timothy Mark Pinkston and** Flich <u>OSé</u> from contribution 0 Interconnection Networks: sentation D major with

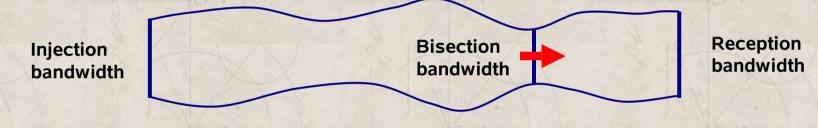

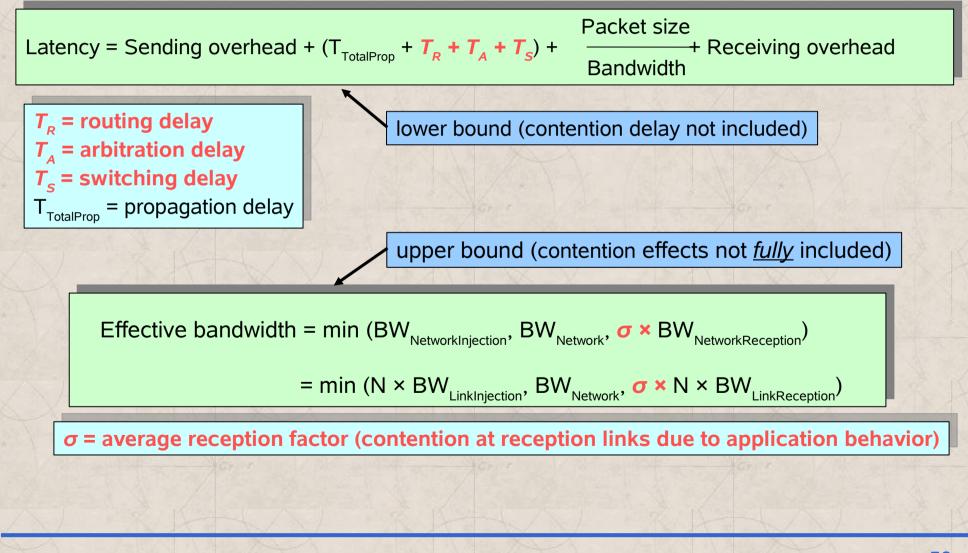

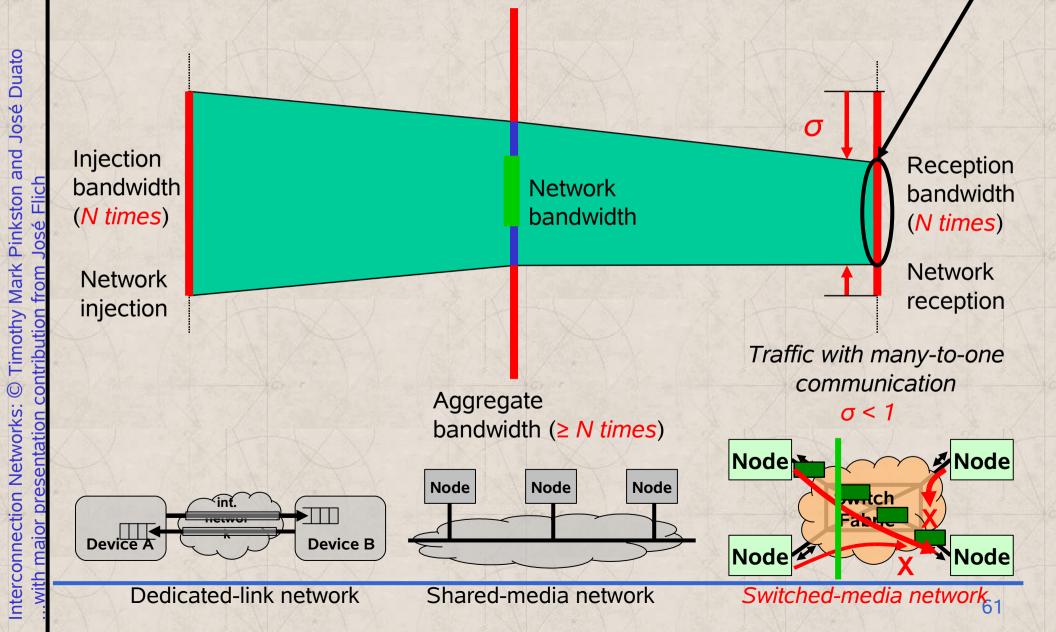

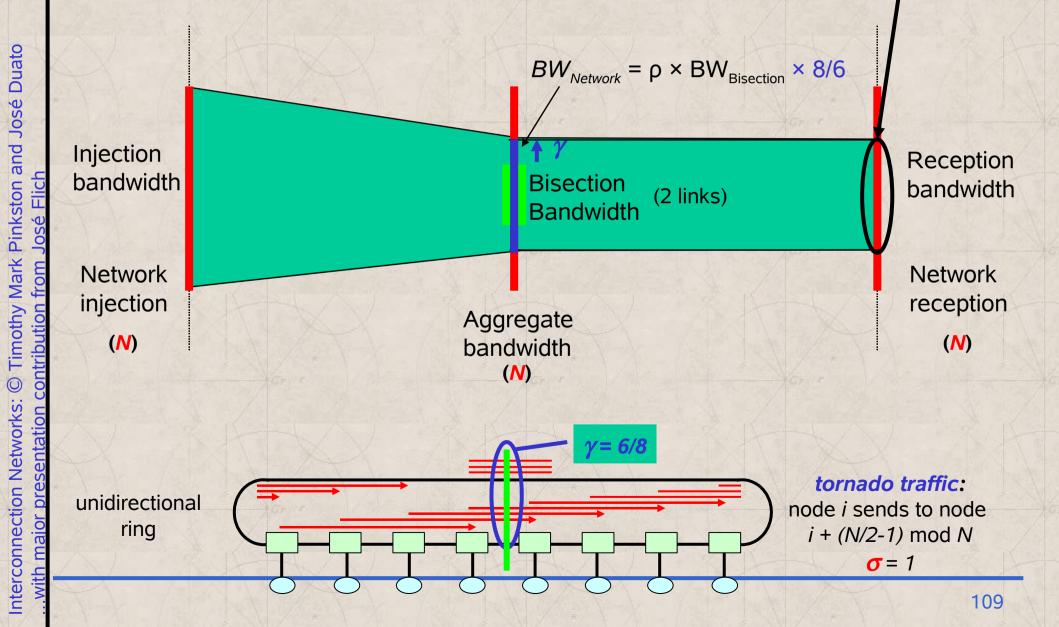

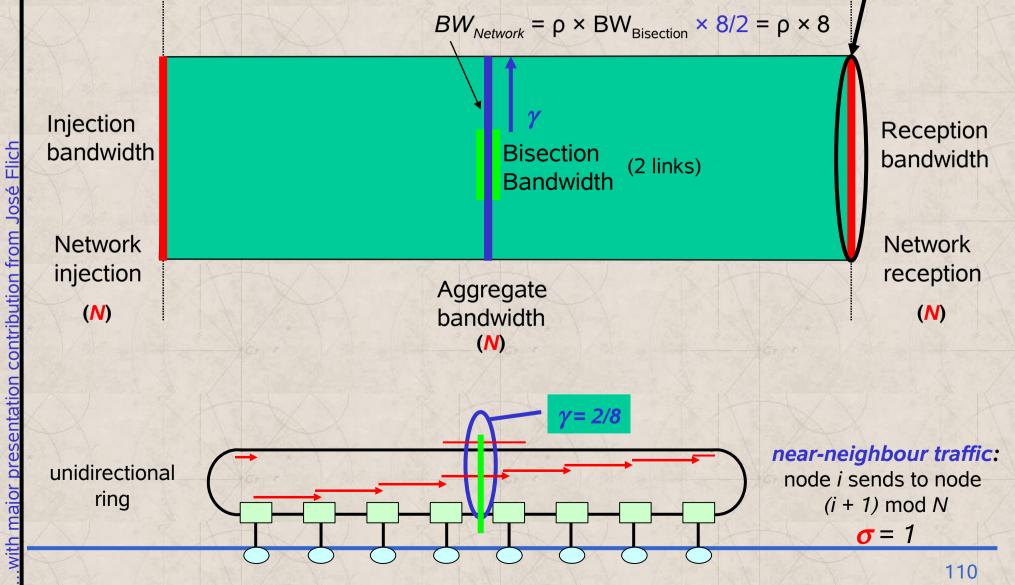

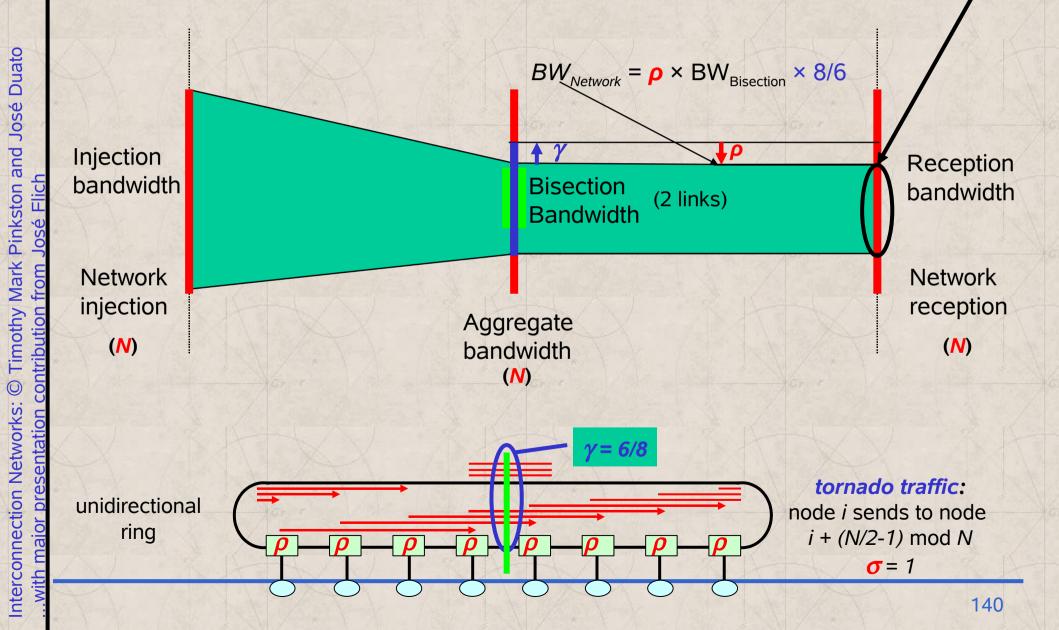

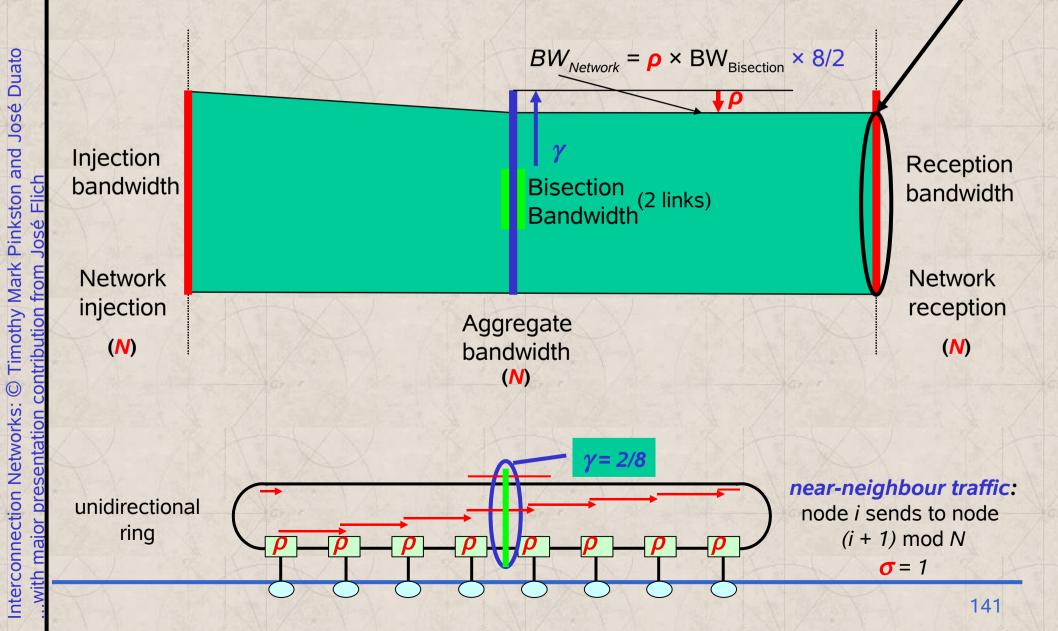

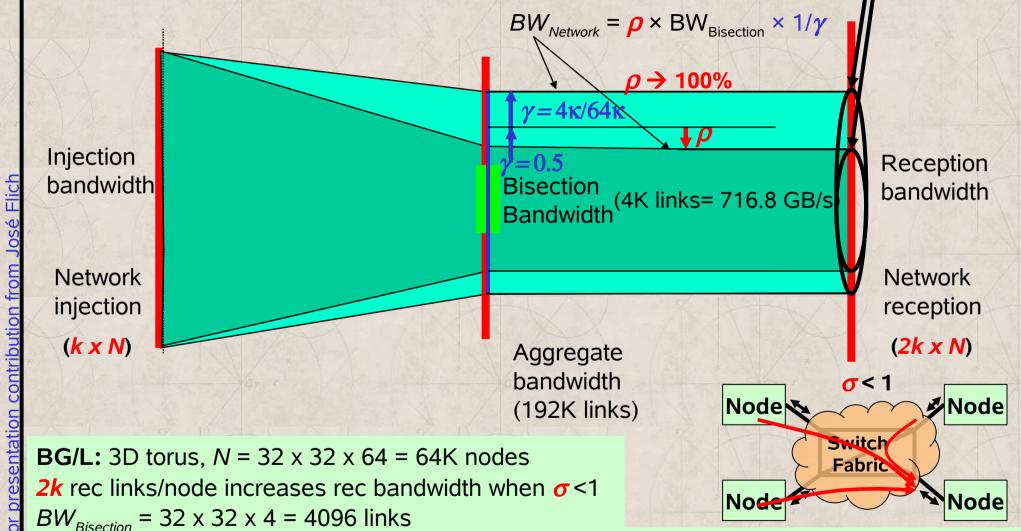

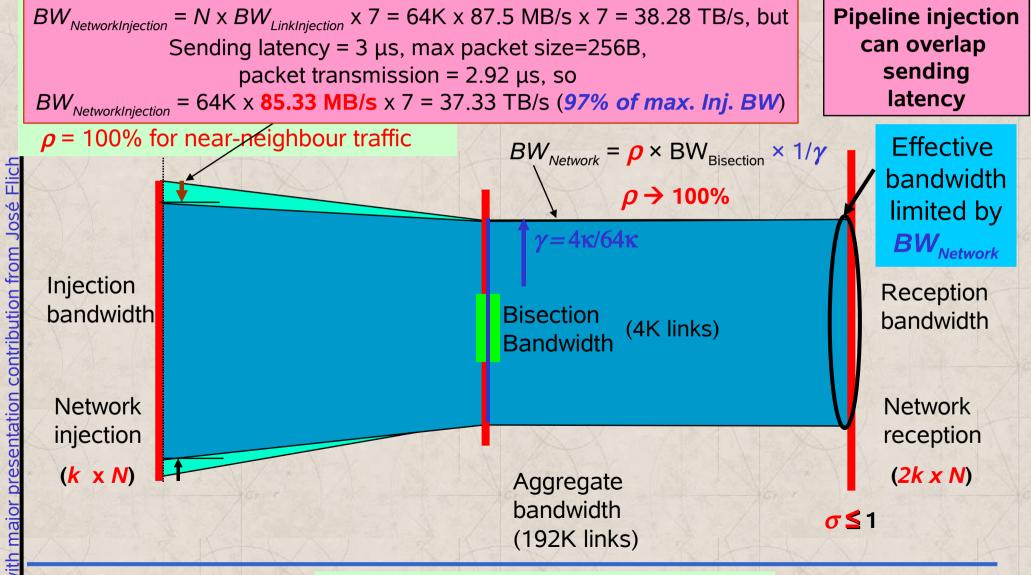

Characterizing Performance: Latency & Effective Bandwidth A Simple (General) Throughput Performance Model:

• The network can be considered as a "pipe" of variable width

- There are three points of interest *end-to-end*:

- Injection into the pipe

- Narrowest section within pipe (i.e., minimum network bisection that has traffic crossing it)

- Reception from the pipe

- The bandwidth at the narrowest point <u>and utilization of that</u> <u>bandwidth</u> determines the throughput!!!

#### Characterizing Performance: Latency & Effective Bandwidth A Simple (General) Throughput Performance Model:

Effective bandwidth =  $min(BW_{NetworkInjection}, BW_{Network}, \sigma \times BW_{NetworkReception})$

$= min(N \times BW_{LinkInjection}, BW_{Network}, \sigma \times N \times BW_{LinkReception})$

ction

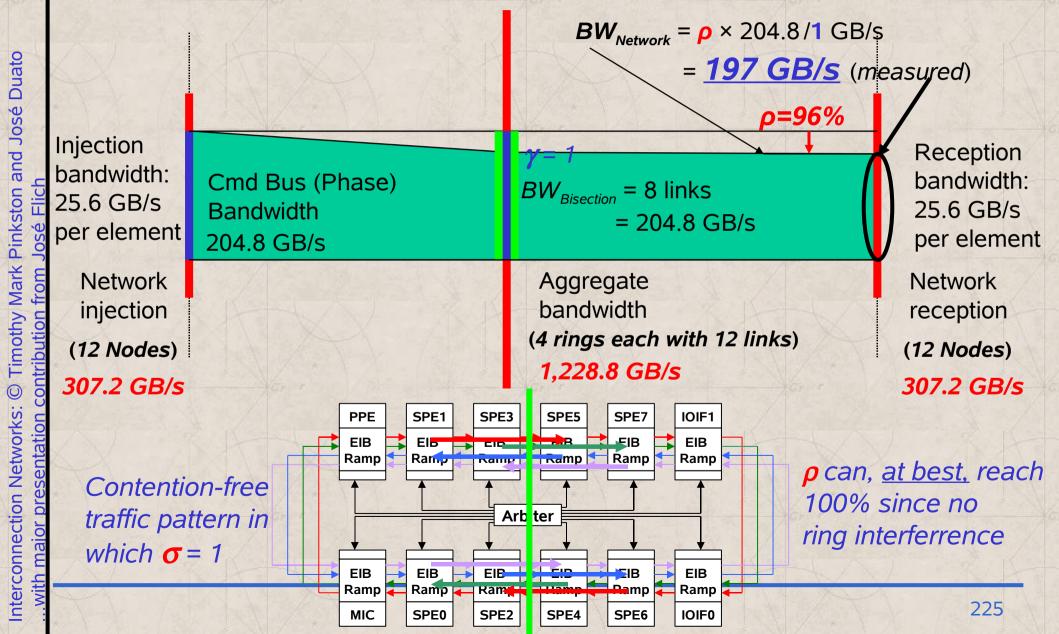

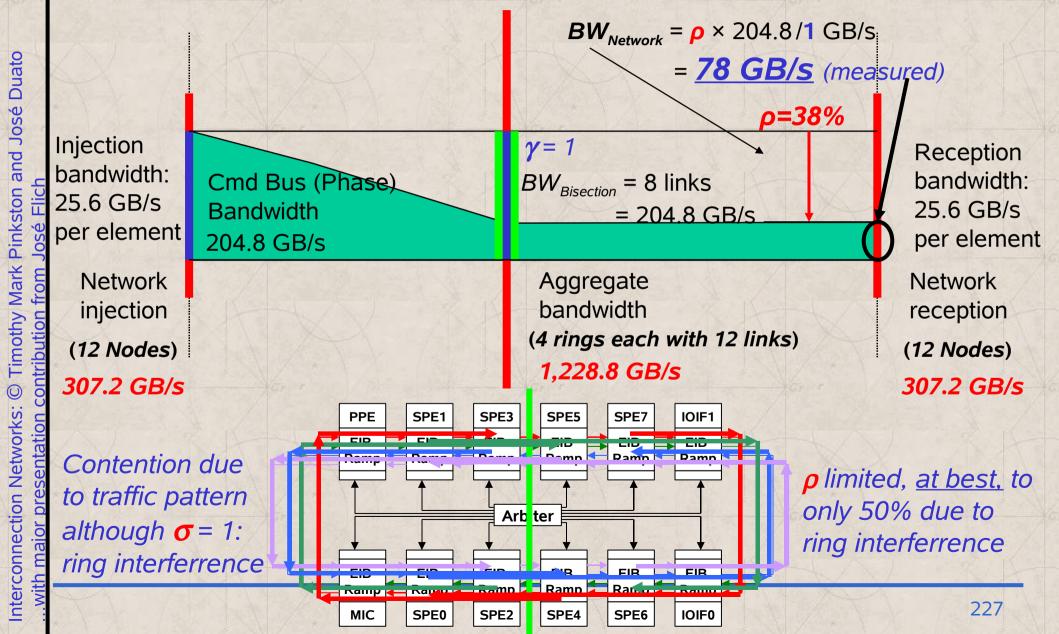

$$BW_{Network} = \rho \times \frac{BW_{Bised}}{\gamma}$$

$\sigma$  is the *ave. fraction of traffic to reception links that can be accepted* (captures contention at reception links due to application behavior)

$\gamma$  is the ave. fraction of traffic that <u>must</u> cross the network bisection

*ρ* is the *network efficiency*, which mostly depends on other factors: *link efficiency, routing efficiency, arb. efficiency, switching eff., etc.*

**BW**<sub>Bisection</sub> is minimum network bisection that has traffic crossing4it

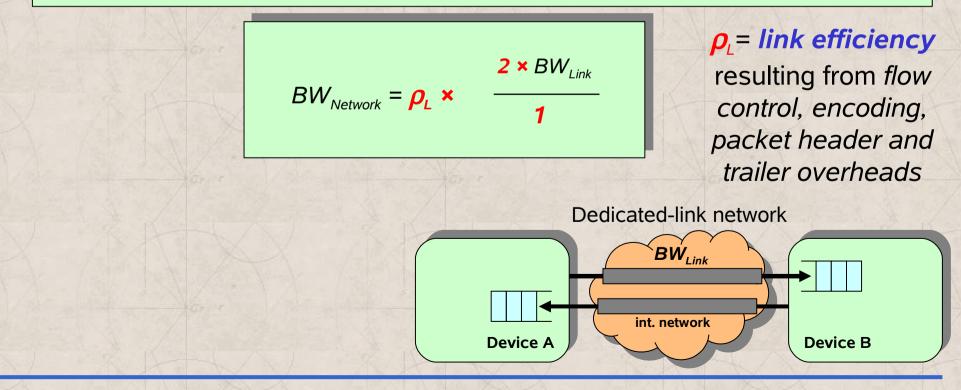

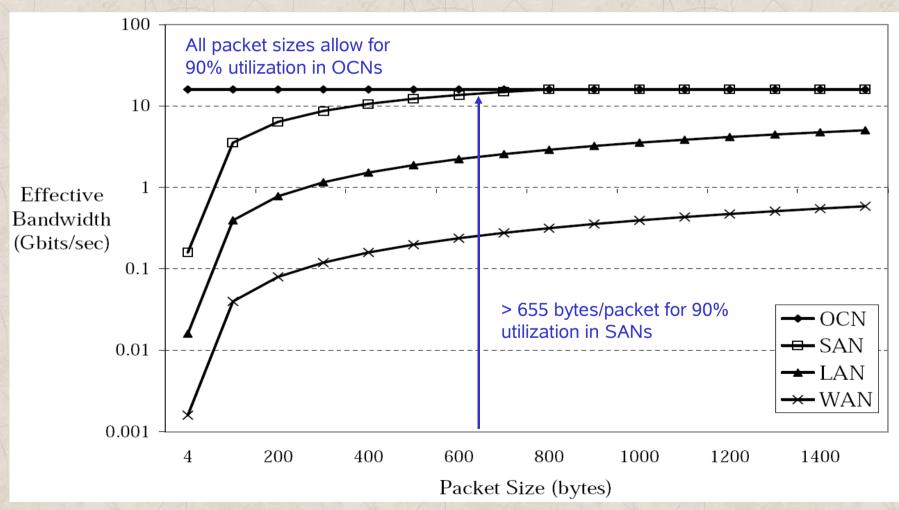

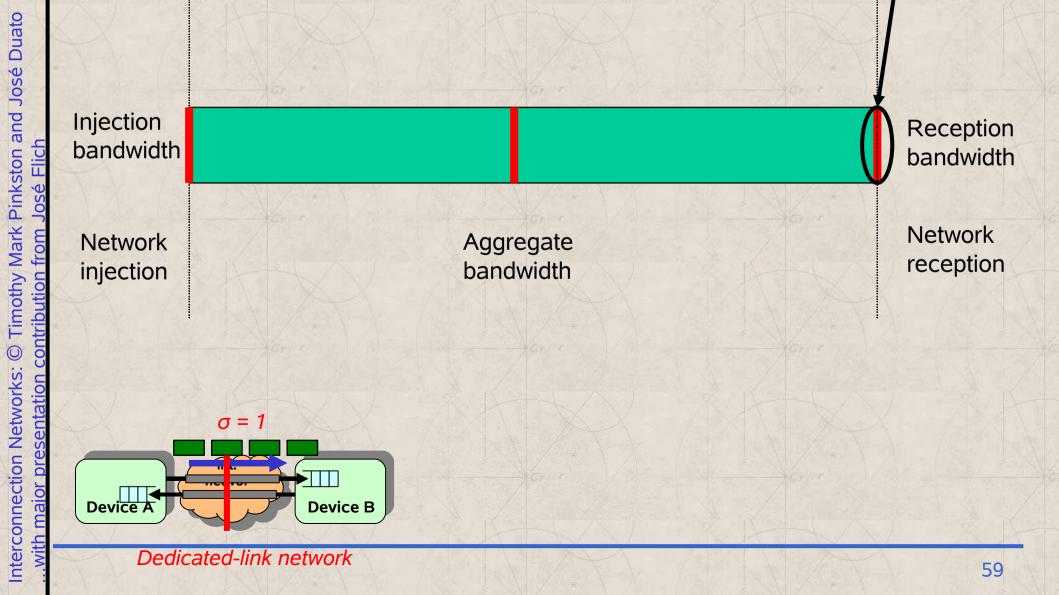

#### Characterizing Performance: Latency & Effective Bandwidth Simple (General) Model Applied to Interconnecting <u>Two Devices</u>:

Effective bandwidth =  $min(BW_{NetworkInjection}, BW_{Network}, \sigma \times BW_{NetworkReception})$

$= min(2 \times BW_{LinkInjection}, BW_{Network}, \mathbf{1} \times (2 \times BW_{LinkReception}))$

- Example: plot the effective bandwidth versus packet size

- Assume a dedicated-link network with

- > 8 Gbps (raw) data bandwidth per link, credit-based flow control

- Packets range in size from 4 bytes to 1500 bytes

- Overheads

- Sending overhead: x + 0.05 ns/byte

- > Receiving overhead: 4/3(x) + 0.05 ns/byte

- > x is 0  $\mu$ s for OCN, 0.3  $\mu$ s for SAN, 3  $\mu$ s for LAN, 30  $\mu$ s for WAN

- What limits the effective bandwidth?

- For what packet sizes is 90% of the aggregate bandwidth utilized?

Dedicated-link network

#### Characterizing Performance: Latency & Effective Bandwidth

• Example: plot the effective bandwidth versus packet size

*Transmission time* is the limiter for OCNs; *overhead* limits SANs for packets sizes < 800 bytes

#### **Basic Network Characteristics of Commercial Machines**

| Compan | y System<br>[Network] Name                 | Intro<br>year | Max.<br>compute<br>nodes<br>[x # CPUs] | System footprint<br>for max.<br>configuration    | Packet<br>[header]<br>max.<br>size | Injection<br>[Recept'n]<br>node BW<br>in<br>Mbytes/s | Minimum<br>send/rec<br>overhead | Maximum<br>copper link<br>length; flow<br>control; error |

|--------|--------------------------------------------|---------------|----------------------------------------|--------------------------------------------------|------------------------------------|------------------------------------------------------|---------------------------------|----------------------------------------------------------|

| Intel  | ASCI Red<br>Paragon                        | 2001          | 4,510<br>[x 2]                         | 2,500 sq. feet                                   | 1984 B<br>[4 B]                    | 400<br>[400]                                         | few<br>µsec                     | handshaking<br>;<br>CRC+parity                           |

| IBM    | ASCI White<br>SP Power3<br>[Colony]        | 2001          | 512<br>[x 16]                          | 10,000 sq. feet                                  | 1024 B<br>[6 B]                    | 500<br>[500]                                         | ~3 µsec                         | 25 m;<br>credit-based;<br>CRC                            |

| Intel  | Thunter Itanium2<br>Tiger4<br>[QsNet"]     | 2004          | 1,024<br>[x 4]                         | 120 m²                                           | 2048 B<br>[14 B]                   | 928<br>[928]                                         | 0.240<br>µsec                   | 13 m;credit-<br>based; CRC<br>for link, dest             |

| Cray   | XT3<br>[SeaStar]                           | 2004          | 30,508<br>[x 1]                        | <b>263.8</b> m <sup>2</sup>                      | 80 B<br>[16 B]                     | 3,200<br>[3,200]                                     | few µsec                        | 7 m; credit-<br>based; CRC                               |

| Cray   | X1E                                        | 2004          | 1,024<br>[x 1]                         | <b>27</b> m²                                     | 32 B<br>[16 B]                     | 1,600<br>[1,600]                                     | ~0 (direct<br>LD/ST<br>acc.)    | 5 m; credit-<br>based; CRC                               |

| ІВМ    | ASC Purple<br>pSeries 575<br>[Federation]  | 2005          | >1,280<br>[x 8]                        | 6,720 sq. feet                                   | 2048 B<br>[7 B]                    | 2,000<br>[2,000]                                     | ~ 1 µsec<br>*                   | 25 m; credit-<br>based; CRC                              |

| IBM    | Blue Gene/L<br>eServer Sol.<br>[Torus Net] | 2005          | 65,536<br>[x 2]                        | 2,500 sq. feet<br>(.9x.9x1.9 m³/1K<br>node rack) | 256 B<br>[8 B]                     | 612,5<br>[1,050]                                     | ~ 3 μsec<br>(2,300<br>cycles)   | 8.6 m; credit-<br>based; CRC<br>(header/pkt)             |

| IBM    | eServer Sol.                               | 2005          |                                        | (.9x.9x1.9 m³/1K                                 |                                    |                                                      | (2,300                          | based                                                    |

\*with up to 4 packets processed in parallel

# Outline

- E.1 Introduction (Lecture 1)

- E.2 Interconnecting Two Devices (Lecture 1)

- E.3 Interconnecting Many Devices (Lecture 2)

- Additional Network Structure and Functions

- Shared-Media Networks

- Switched-Media Networks

- Comparison of Shared- versus Switched-Media Networks

- Characterizing Performance: Latency & Effective Bandwidth

- E.4 Network Topology (Lecture 2)

- E.5 Network Routing, Arbitration, and Switching (Lecture 3)

- E.6 Switch Microarchitecture (Lecture 4)

- E.7 Practical Issues for Commercial Interconnection Networks (Lec 4)

- E.8 Examples of Interconnection Networks (Lecture 5)

- E.9 Internetworking (skipped)

- E.10 Crosscutting Issues for Interconnection Networks (skipped)

- E.11 Fallacies and Pitfalls (Lecture 5)

- E.12 Concluding Remarks and References (Lecture 5)

#### **Additional Network Structure and Functions**

- Basic network structure and functions

- Composing and processing messages, packets

- Media and form factor

- Packet transport

- Reliable delivery (e.g., flow control) and error handling

- Additional structure

- Topology

- > What paths are possible for packets?

- Networks usually share paths among different pairs of devices

- Additional functions (*routing*, *arbitration*, *switching*)

- Required in every network connecting more than two devices

- Required to establish a valid path from source to destination

- Complexity and applied order depends on the category of the topology: *shared-media* or *switched media*

#### Additional Network Structure and Functions

- Additional functions (routing, arbitration, switching)

- Routing

- > Which of the possible paths are allowable (valid) for packets?

- > Provides the set of operations needed to compute a valid path

- > Executed at source, intermediate, or even at destination nodes

- Arbitration

- > When are paths available for packets? (along with flow control)

- > Resolves packets requesting the same resources at the same time

- > For every arbitration, there is a winner and possibly many losers

- » Losers are buffered (lossless) or dropped on overflow (lossy)

- Switching

- > How are paths allocated to packets?

- > The winning packet (from arbitration) proceeds towards destination

- > Paths can be established one fragment at a time or in their entirety

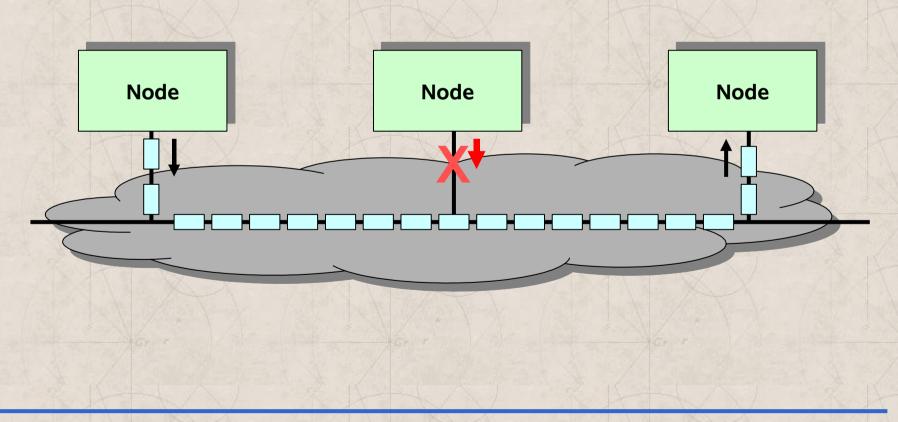

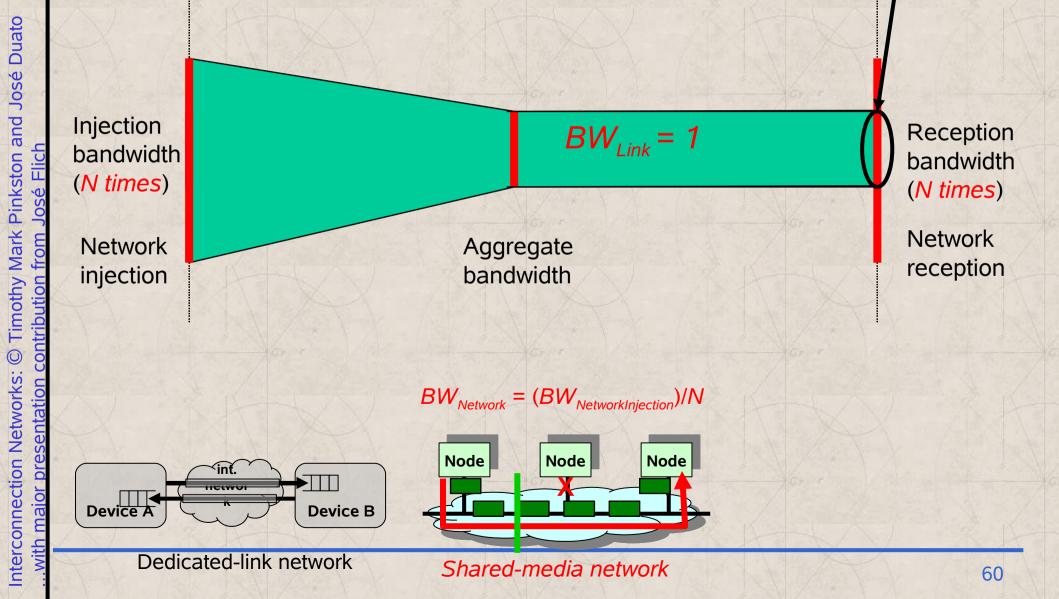

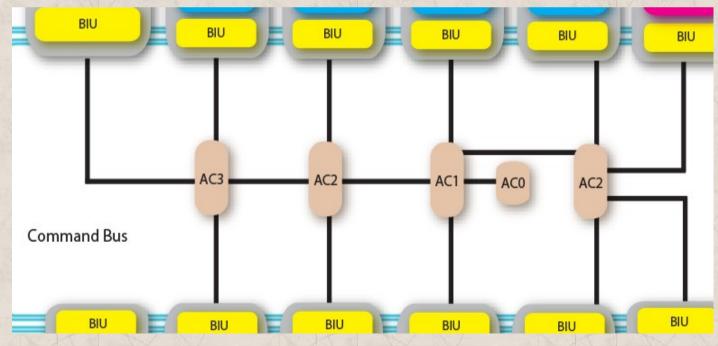

#### Shared-media Networks

- The network media is shared by all the devices

- Operation: half-duplex or full-duplex

Duato José Timothy Mark Pinkston and Flich 0Sé from contribution 0 Interconnection Networks: sentation D maior with

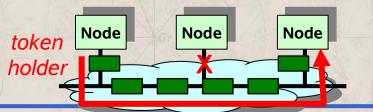

#### Shared-media Networks

- Arbitration

- Centralized arbiter for smaller distances between devices

- Dedicated control lines

- Distributed forms of arbiters

- > CSMA/CD

- » The device first checks the network (carrier sensing)

- » Then checks if the data sent was garbled (collision detection)

- » If collision, device must send data again (retransmission): wait an increasing exponential random amount of time beforehand

- » Fairness is not guaranteed

- > Token ring—provides fairness

- » Owning the token provides permission to use network media

#### Shared-media Networks

- Switching

- Switching is straightforward

- The granted device connects to the shared media

- Routing

- Routing is straightforward

- Performed at all the potential destinations

- > Each end node device checks whether it is the target of the packet

- Broadcast and multicast is easy to implement

- > Every end node devices sees the data sent on shared link anyway

- Established order: arbitration, switching, and <u>then</u> routing

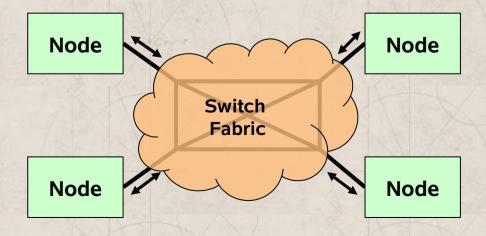

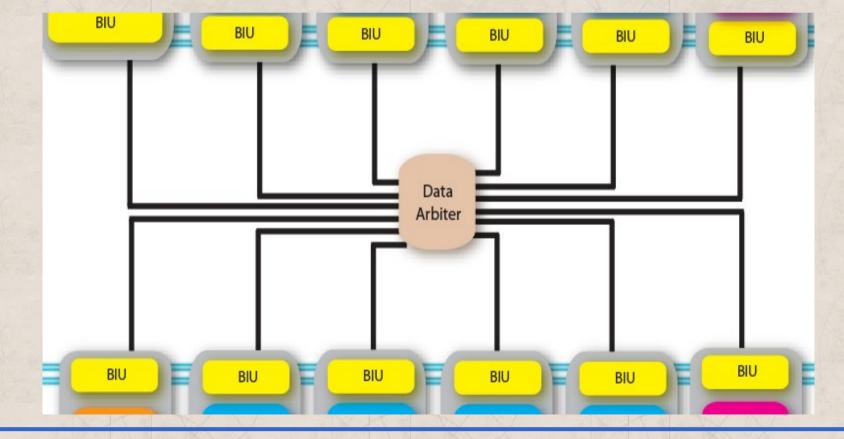

#### Switched-media Networks

- Disjoint portions of the media are shared via switching

- Switch fabric components

- Passive point-to-point links

- Active *switches*

- Dynamically establish communication between sets of sourcedestination pairs

- Aggregate bandwidth can be many times higher than that of shared-media networks

#### Switched-media Networks

- Routing

- Every time a packet enters the network, it is routed

- Arbitration

- Centralized or distributed

- Resolves conflicts among concurrent requests

- Switching

- Once conflicts are resolved, the network "switches in" the required connections

- Established order: routing, arbitration, and *then* switching

#### Comparison of Shared- versus Switched-media Networks

- Shared-media networks

- Low cost

- Aggregate network bandwidth does not scale with # of devices

- Global arbitration scheme required (a possible bottleneck)

- Time of flight increases with the number of end nodes

- Switched-media networks

- Aggregate network bandwidth scales with number of devices

- Concurrent communication

- > Potentially much higher network effective bandwidth

- Beware: inefficient designs are quite possible

- > Superlinear network cost but sublinear network effective bandwidth

Timothy Mark Pinkston and José Duato

Flich

losé

from

contribution

sentation

major pre

with

Interconnection Networks: ©

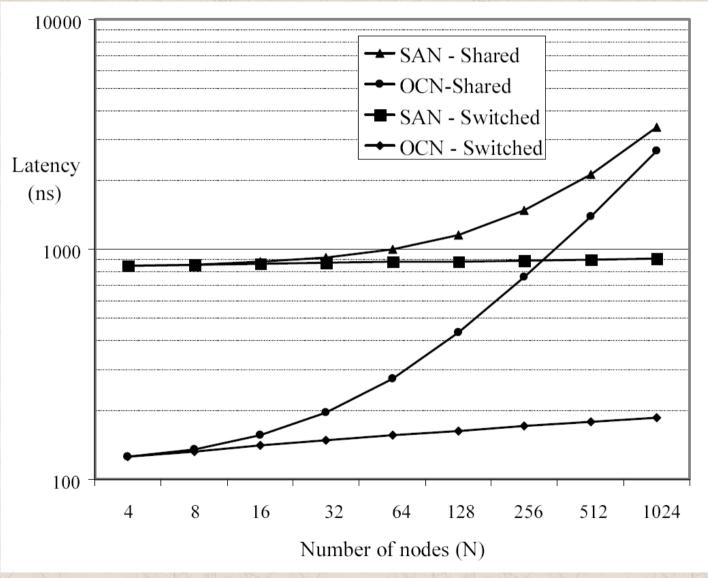

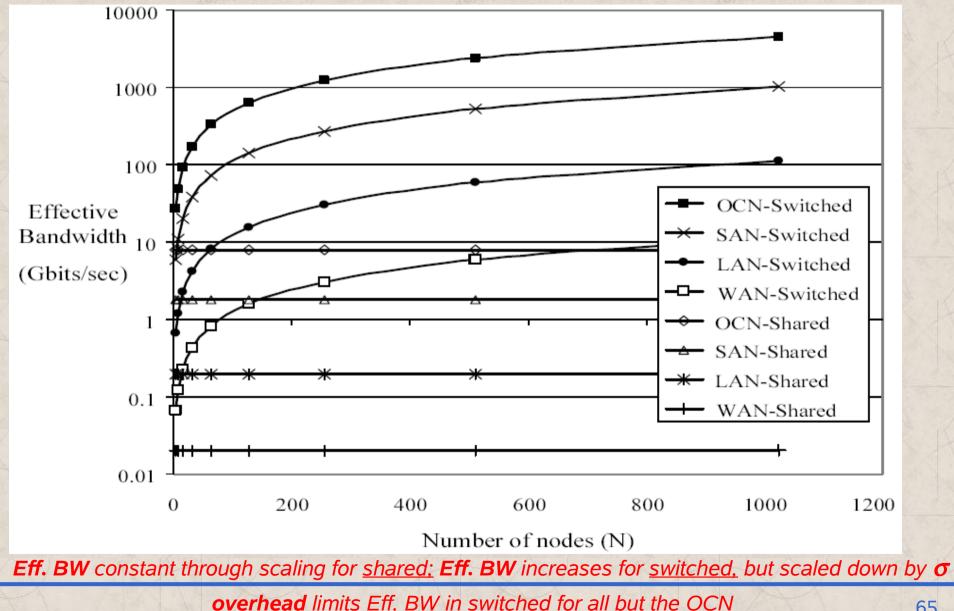

#### **Characterizing Performance: Latency & Effective Bandwidth**

Characteristic performance plots: latency vs. average load rate; throughput (effective bandwidth) vs. average load rate

- Example: plot the total packet latency and effective bandwidth

- Assume N scales from 4 to 1024 end nodes and the following:

- Shared media (one link) and switched media (N links)

- All network links have data bandwidth of 8 Gbps

- Unicast transmission of packets of size 100 bytes

- Overheads

- > sending: x + 0.05 ns/byte; receiving: 4/3(x) + 0.05 ns/byte

- > x is 0 for OCNs, 0.3  $\mu$ s for SANs, 3  $\mu$ s for LANs, 30  $\mu$ s for WANs

- Distances: 0.5 cm, 5 m, 5,000 m, and 5,000 km

- Routing, Arbitration, and Switching

- > shared media:  $T_R = 2.5$  ns,  $T_A = 2.5(N)$  ns,  $T_S = 2.5$  ns

- > switched media:  $T_R = T_A = T_S = 2.5 (\log_2 N)$  ns

- $-\sigma = N^{-1}$  (shared),  $\sigma = (\log_2 N)^{-1/4}$  (switched)

#### **Characterizing Performance: Latency & Effective Bandwidth**

• For OCNs,  $T_R$ ,  $T_A$ , and  $T_s$  combine to dominate time of flight delay and are >> than other latency components for all network sizes.

• For SANs,  $T_R$ ,  $T_A$ , and  $T_s$  combine to dominate time of flight delay but are less than other latency components for switched-media (but not negligibly so)

• For LANs and WANs, latency is dominated by propagation delay, *T*<sub>Prop</sub>

# Outline

- E.1 Introduction (Lecture 1)

- E.2 Interconnecting Two Devices (Lecture 1)

- E.3 Interconnecting Many Devices (Lecture 2)

- E.4 Network Topology (Lecture 2)

- Preliminaries and Evolution

- Centralized Switched (Indirect) Networks

- Distributed Switched (Direct) Networks

- Comparison of Indirect and Direct Networks

- Characterizing Performance: Latency & Effective Bandwidth

- E.5 Network Routing, Arbitration, and Switching (Lecture 3)

- E.6 Switch Microarchitecture (Lecture 4)

- E.7 Practical Issues for Commercial Interconnection Networks (Lecture 4)

- E.8 Examples of Interconnection Networks (Lecture 5)

- E.9 Internetworking (skipped)

- E.10 Crosscutting Issues for Interconnection Networks (skipped)

- E.11 Fallacies and Pitfalls (Lecture 5)

- E.12 Concluding Remarks and References (Lecture 5)

#### **Preliminaries and Evolution**

- One switch suffices to connect a small number of devices

- Number of switch ports limited by VLSI technology, power consumption, packaging, and other such *cost* constraints

- A *fabric* of interconnected switches (i.e., *switch fabric* or *network fabric*) is needed when the number of devices is much larger

- The topology must make a path(s) available for every pair of devices—property of connectedness or full access (What paths?)

- Topology defines the connection structure across all components

- Bisection bandwidth: the minimum bandwidth of all links crossing a network split into two roughly equal halves

- Full bisection bandwidth:

- > Network  $BW_{Bisection} =$  Injection (or Reception)  $BW_{Bisection} = N/2$

- Bisection bandwidth mainly affects performance

- Topology is constrained primarily by local chip/board pin-outs; secondarily, (if at all) by global bisection bandwidth

#### **Preliminaries and Evolution**

- Several tens of topologies proposed, but less than a dozen used

- 1970s and 1980s

- Topologies were proposed to reduce hop count

- 1990s

- Pipelined transmission and switching techniques

- Packet latency became decoupled from hop count

- 2000s

- Topology still important (especially OCNs, SANs) when N is high

- Topology impacts performance and has a major impact on cost

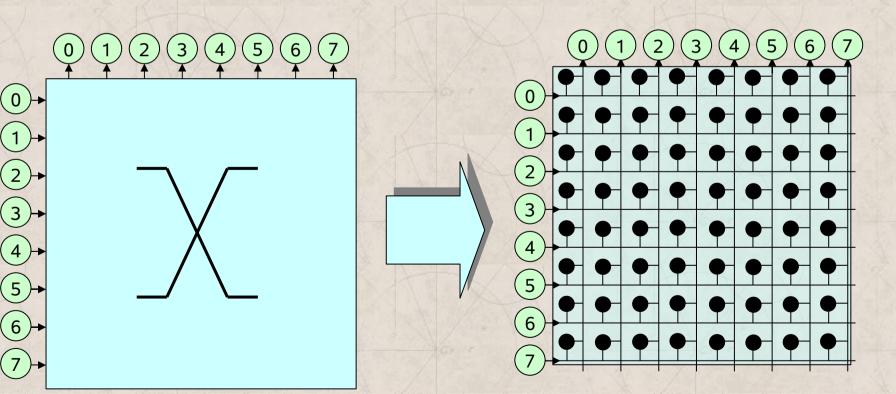

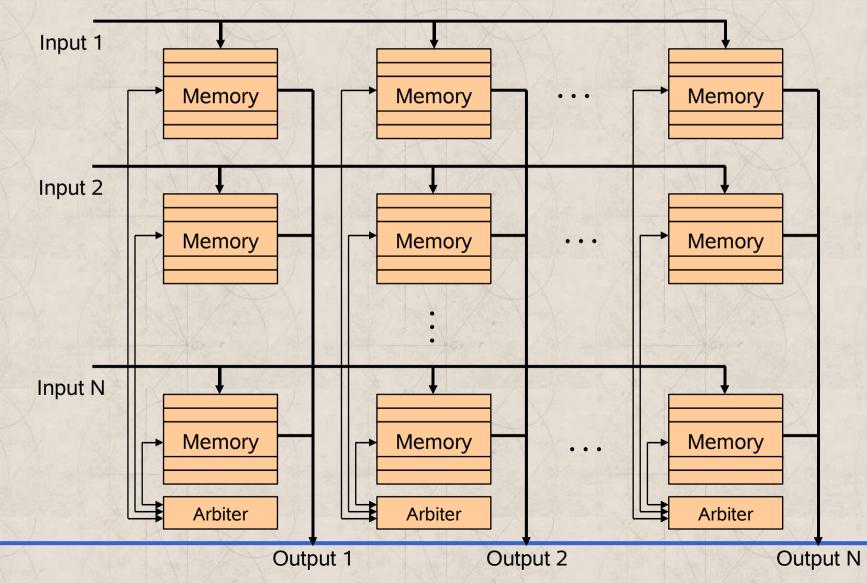

#### Centralized Switched (Indirect) Networks

- Crossbar network

- Crosspoint switch complexity increases quadratically with the number of crossbar input/output ports, N, i.e., grows as  $O(N^2)$

- Has the property of being *non-blocking*

Centralized Switched (Indirect) Networks

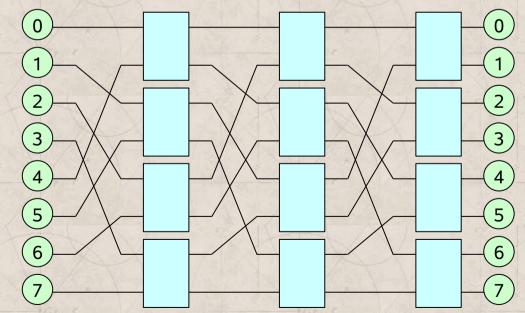

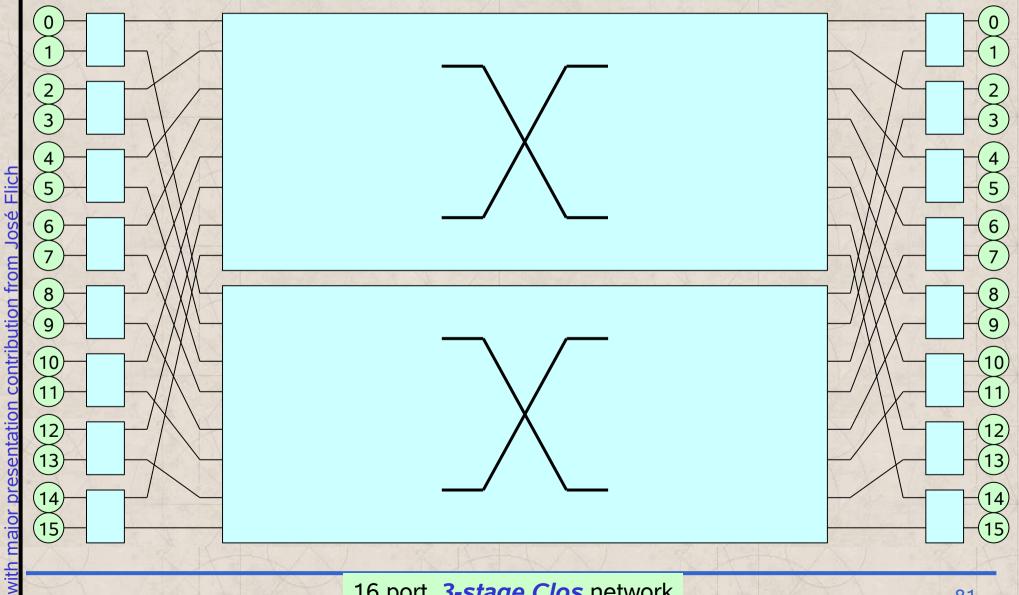

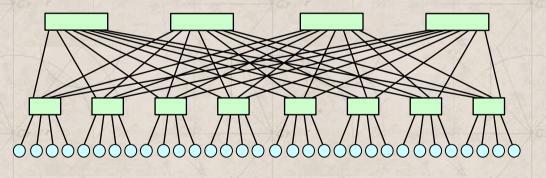

- Multistage interconnection networks (MINs)

- Crossbar split into several stages consisting of smaller crossbars

- Complexity grows as  $O(N \times \log N)$ , where N is # of end nodes

- Inter-stage connections represented by a set of permutation functions

Omega topology, perfect-shuffle exchange

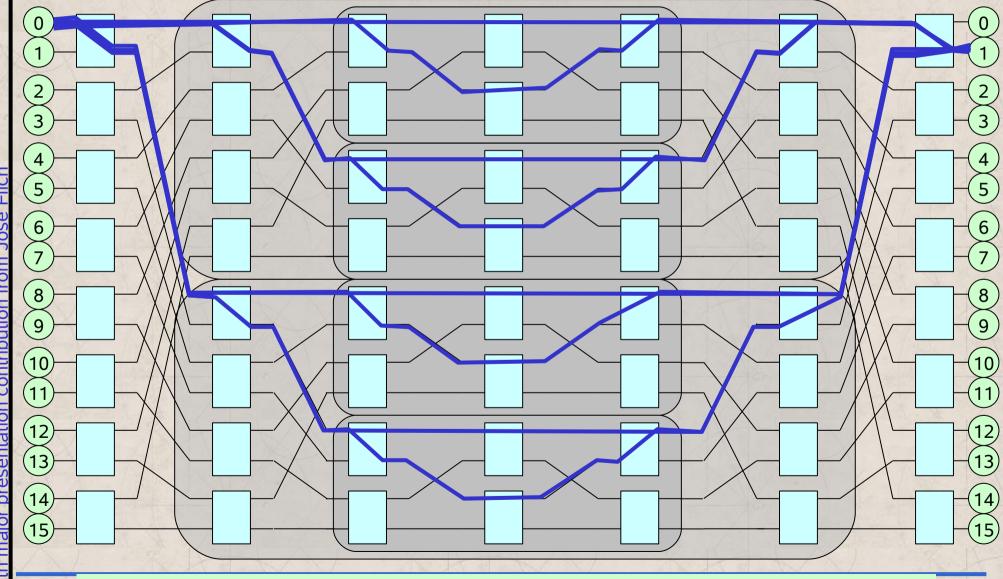

#### Centralized Switched (Indirect) Networks

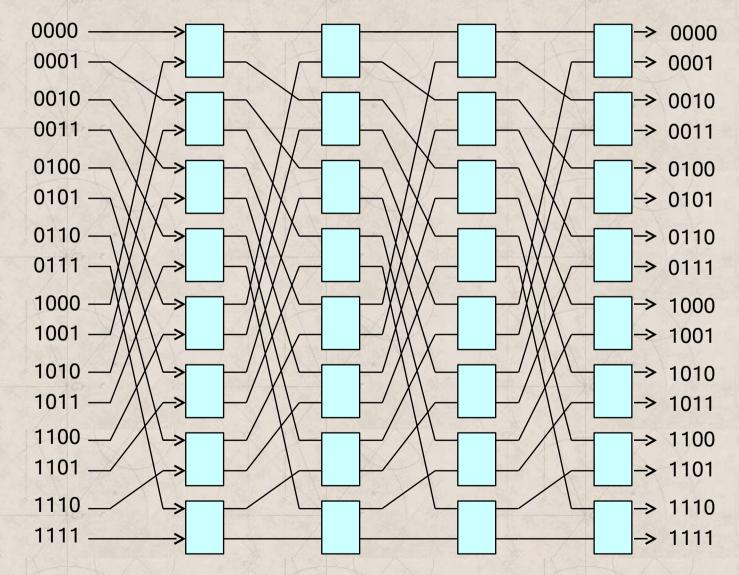

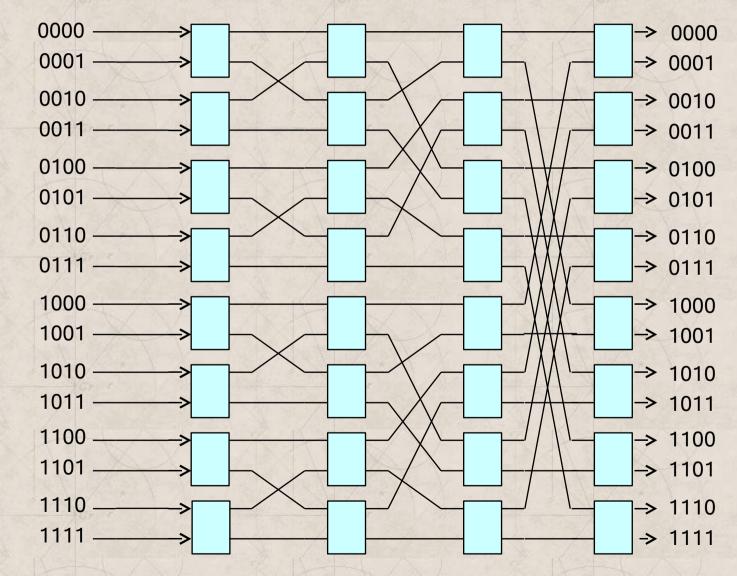

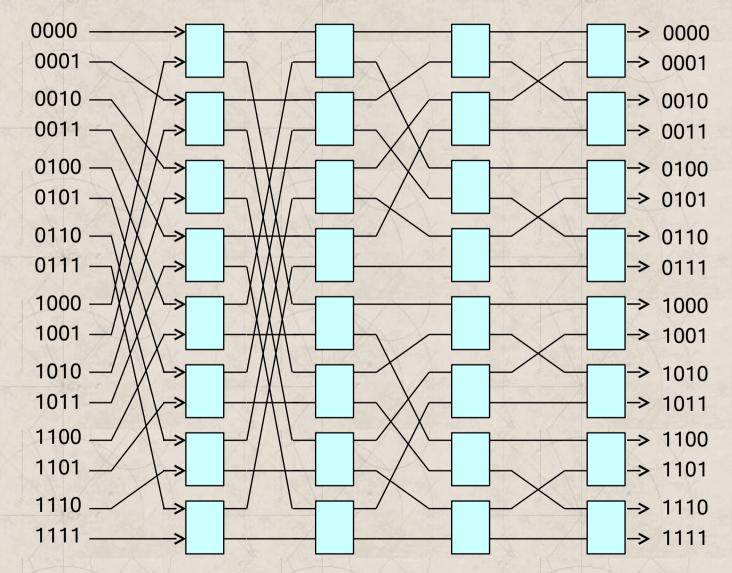

16 port, 4 stage Omega network

#### Centralized Switched (Indirect) Networks

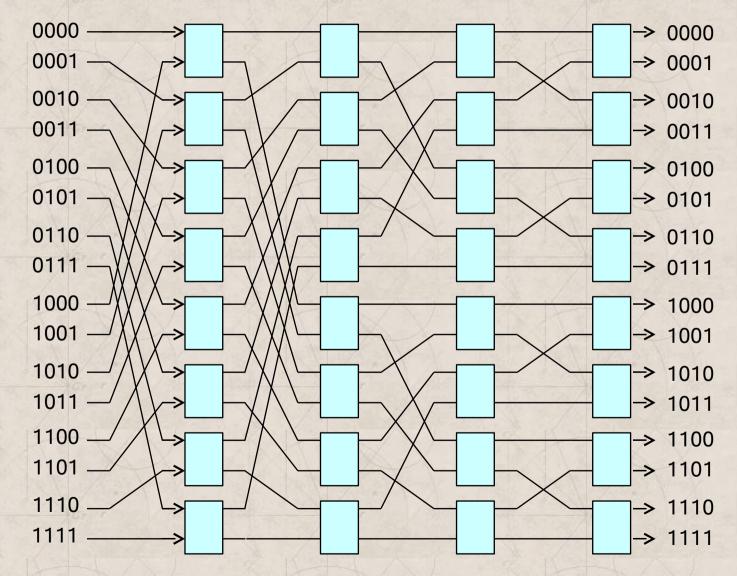

16 port, 4 stage **Baseline** network

#### Centralized Switched (Indirect) Networks

16 port, 4 stage **Butterfly** network

#### Centralized Switched (Indirect) Networks

16 port, 4 stage Cube network

- Multistage interconnection networks (MINs)

- MINs interconnect N input/output ports using k x k switches

- >  $\log_k N$  switch stages, each with N/k switches

- >  $N/k(\log_k N)$  total number of switches

- *Example:* Compute the switch and link costs of interconnecting 4096 nodes using a crossbar relative to a MIN, assuming that switch cost grows quadratically with the number of input/output ports (*k*). Consider the following values of *k*:

- > MIN with 2 x 2 switches

- > MIN with 4 x 4 switches

- > MIN with 16 x 16 switches

#### Centralized Switched (Indirect) Networks

• Example: compute the relative switch and link costs, *N* = 4096

$cost(crossbar)_{switches} = 4096^{2}$  $cost(crossbar)_{links} = 8192$

relative\_cost(2 × 2)<sub>switches</sub> =  $4096^2 / (2^2 \times 4096/2 \times \log_2 4096) = 170$ relative\_cost(2 × 2)<sub>links</sub> =  $8192 / (4096 \times (\log_2 4096 + 1)) = 2/13 = 0.1538$

relative\_cost(4 × 4)<sub>switches</sub> = 4096<sup>2</sup> / (4<sup>2</sup> × 4096/4 × log<sub>4</sub> 4096) = **170** relative\_cost(4 × 4)<sub>links</sub> = 8192 / (4096 × (log<sub>4</sub> 4096 + 1)) = 2/7 = **0.2857**

relative\_cost(16 × 16)<sub>switches</sub> = 4096<sup>2</sup> / (16<sup>2</sup> × 4096/16 × log<sub>16</sub> 4096) = **85** relative\_cost(16 × 16)<sub>links</sub> = 8192 / (4096 × (log<sub>16</sub> 4096 + 1)) = 2/4 = **0.5**

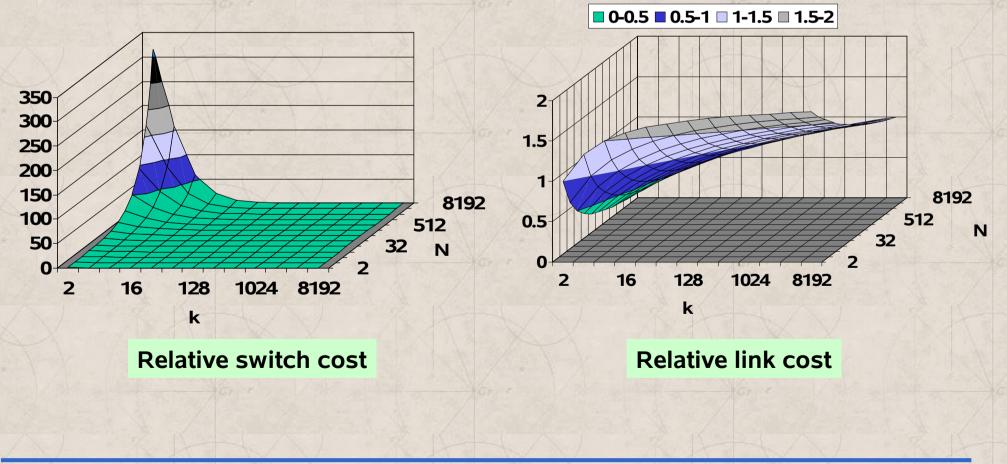

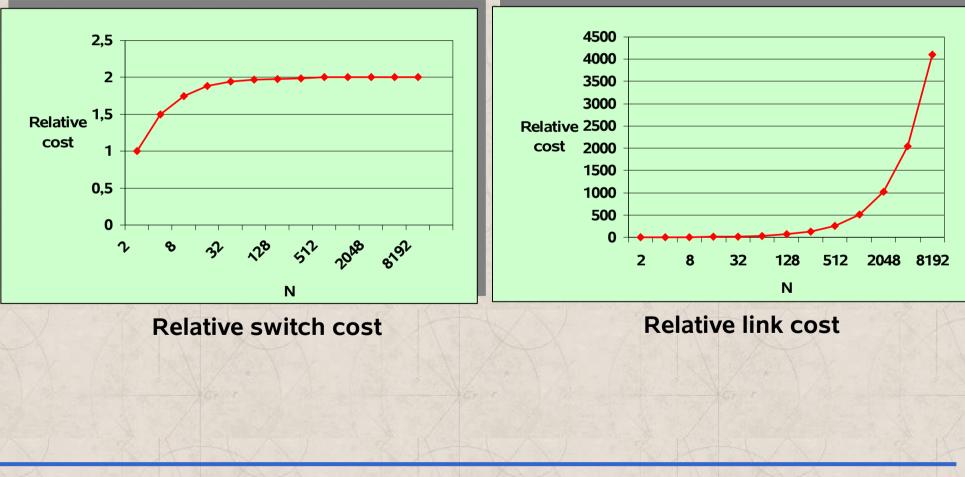

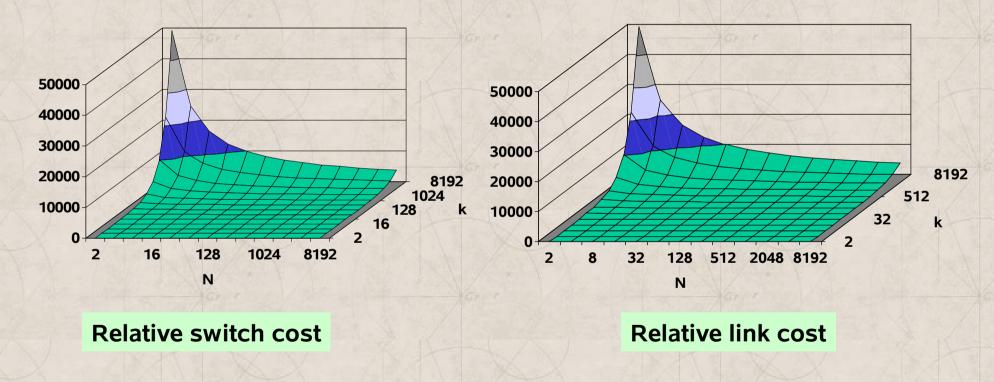

### Centralized Switched (Indirect) Networks

• Relative switch and link costs for various values of *k* and *N* (crossbar relative to a MIN)

Duato José **Timothy Mark Pinkston and** osé Flich from contribution Interconnection Networks: © sentation pre major with

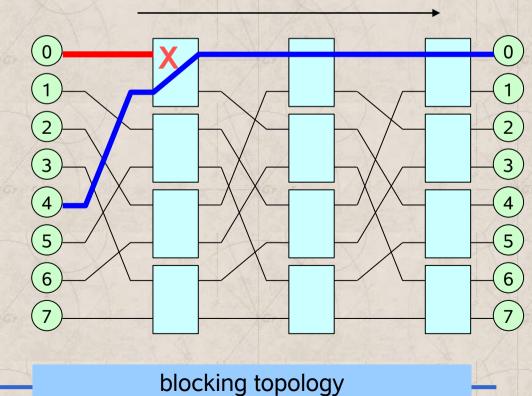

- Reduction in MIN switch <u>cost</u> comes at the price of <u>performance</u>

- Network has the property of being *blocking*

- Contention is more likely to occur on network links

- Paths from different sources to different destinations share one or more links

### Centralized Switched (Indirect) Networks

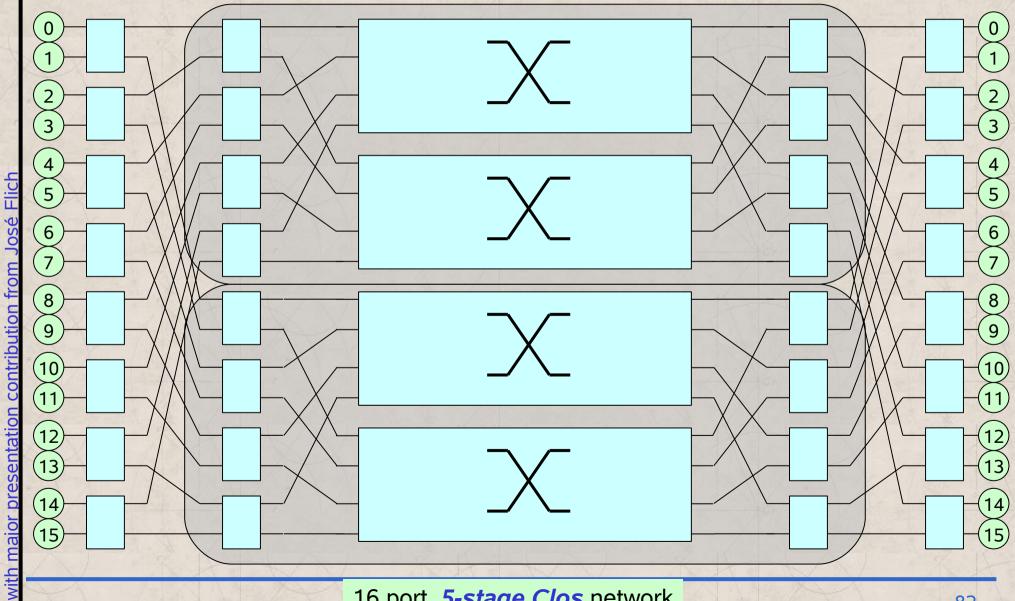

- How to reduce blocking in MINs? Provide alternative paths!

- Use larger switches (can equate to using more switches)

- > Clos network: minimally three stages (non-blocking)

- » A larger switch in the middle of two other switch stages provides enough alternative paths to avoid all conflicts

- Use more switches

- > Add  $\log_k N$  1 stages, mirroring the original topology

- » Rearrangeably non-blocking

- » Allows for non-conflicting paths

- » Doubles network hop count (distance), d

- » Centralized control can rearrange established paths

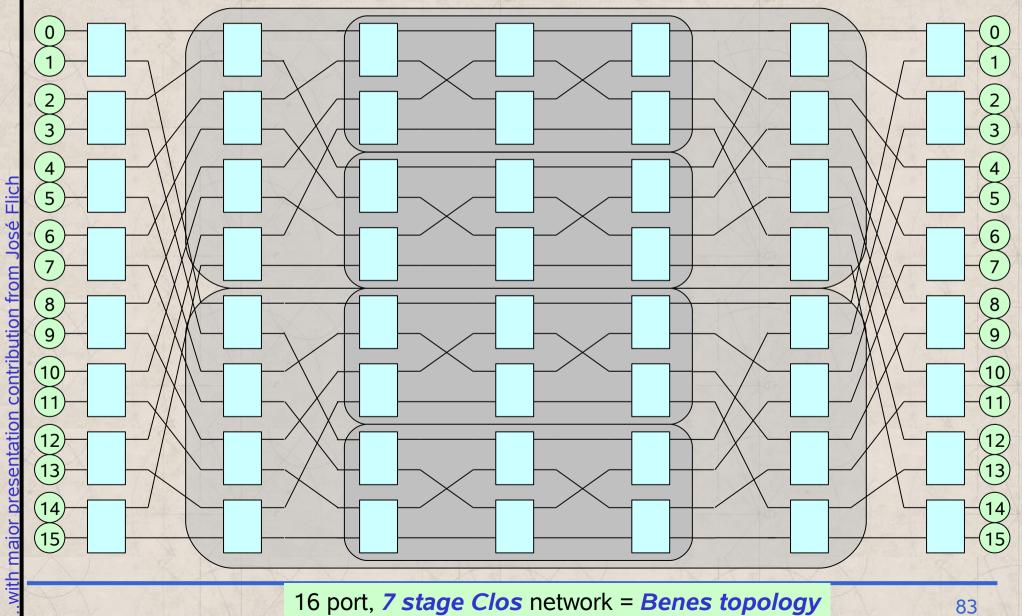

Benes topology: 2(log<sub>2</sub>N) - 1 stages (rearrangeably non-blocking)

» Recursively applies the three-stage Clos network concept to the middle-stage set of switches to reduce all switches to 2 x 2

Interconnection Networks: © Timothy Mark Pinkston and José Duato

Interconnection Networks: © Timothy Mark Pinkston and José Duato

Timothy Mark Pinkston and José Duato

Interconnection Networks: ©

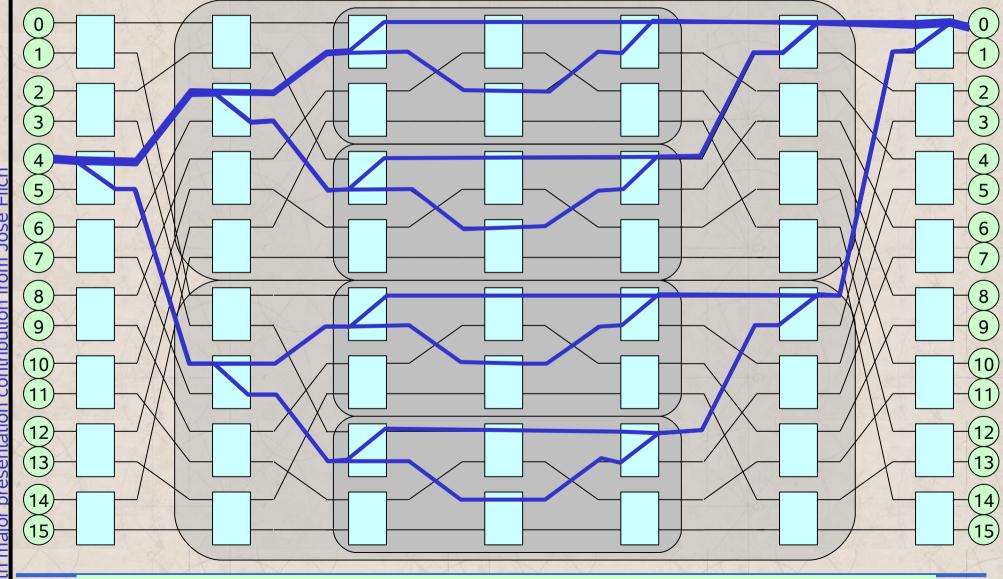

### Centralized Switched (Indirect) Networks

Alternative paths from 0 to 1. 16 port, 7 stage Clos network = Benes topology 84

### Centralized Switched (Indirect) Networks

Alternative paths from 4 to 0. 16 port, 7 stage Clos network = Benes topology 85

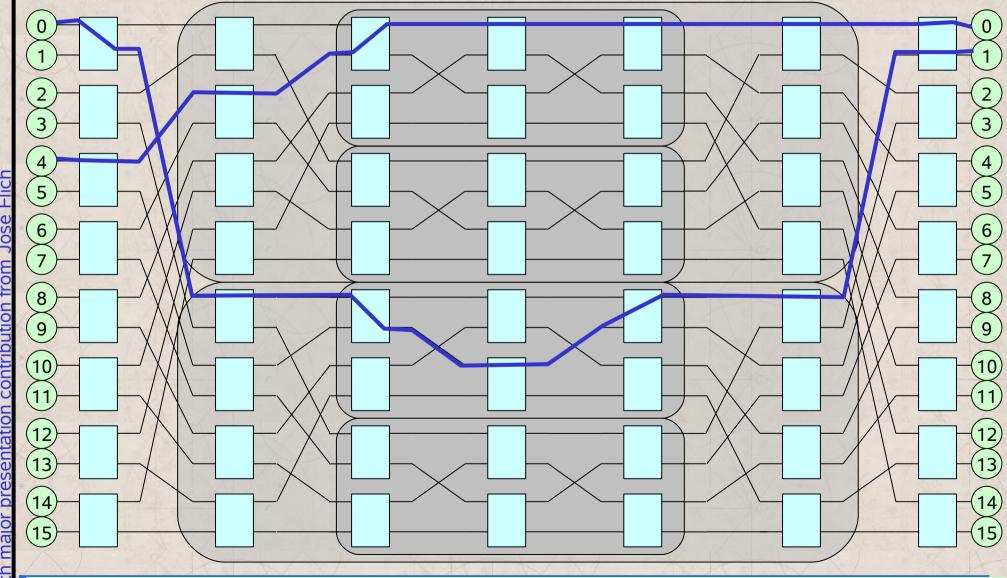

### Centralized Switched (Indirect) Networks

Contention free, paths 0 to 1 and 4 to 1. 16 port, 7 stage Clos network = Benes topology

### Centralized Switched (Indirect) Networks

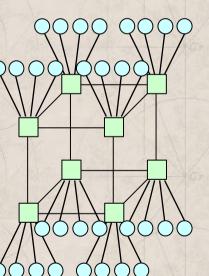

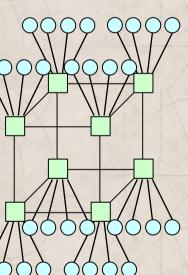

- Bidirectional MINs

- Increase modularity

- Reduce hop count, d

- Fat tree network

- Nodes at tree leaves

- Switches at tree vertices

- Total link bandwidth is constant across all tree levels, with *full bisection bandwidth*

- Equivalent to folded Benes topology

- Preferred topology in many SANs

#### Folded Clos = Folded Benes = Fat tree network 87

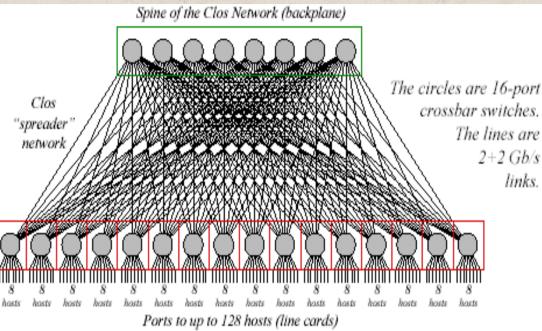

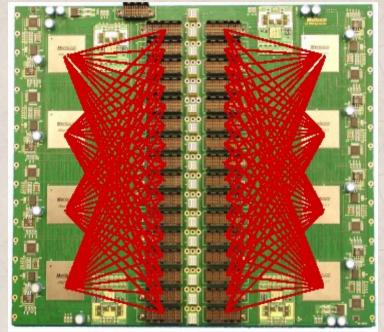

### Myrinet-2000 Clos Network for 128 Hosts

Backplane of the M3-E128 Switch

M3-SW16-8F fiber line card (8 ports)

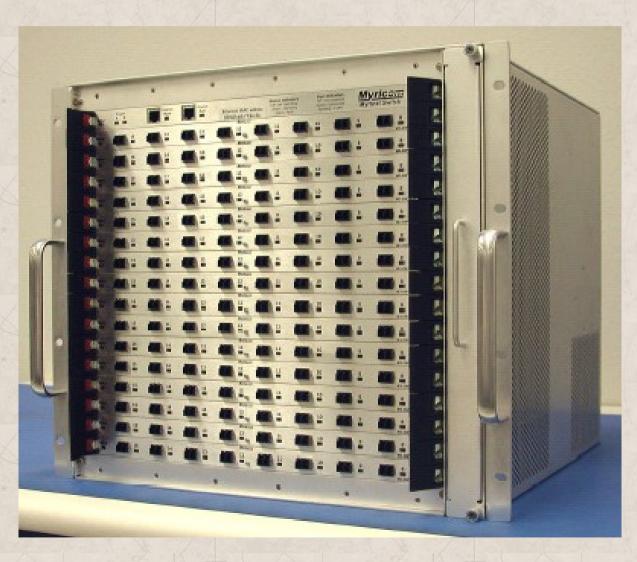

#### Myrinet-2000 Clos Network for 128 Hosts

"Network in a Box"

16 fiber line cards connected to the M3-E128 Switch backplane

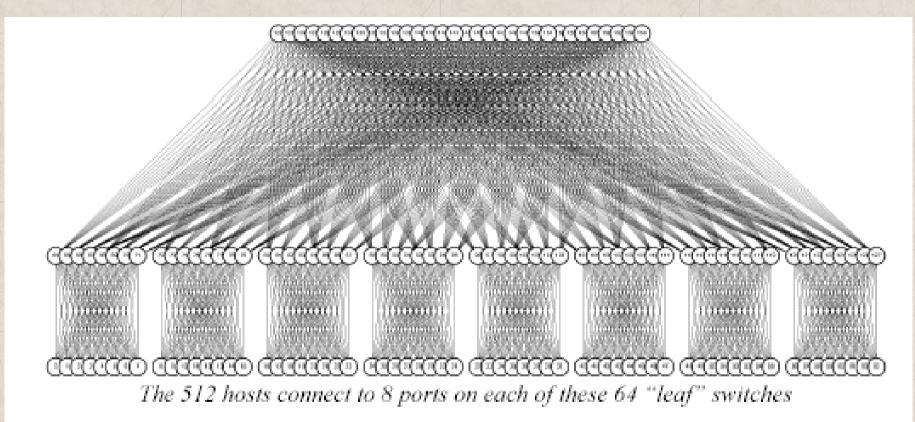

### Myrinet-2000 Clos Network Extended to 512 Hosts

- 160 16-port switches (2,560 switch ports); 1,024 switch-to-switch links; diameter 5.

- The bisection data rate (total throughput) is 1.024 Terabits/s (128 GigaBytes/s).

- This network is <u>routine</u> today, and can scale at a similar cost/host to 8,192 hosts.

- Tight integration of end node devices with network resources

- Network switches distributed among end nodes

- A "node" now consists of a network switch with <u>one or more</u> <u>end node devices directly connected</u> to it

- Nodes are directly connected to other nodes

- Fully-connected network: all nodes are directly connected to all other nodes using bidirectional dedicated links

- *Example:* Compute the switch and link costs of interconnecting *N* nodes using a fully connected topology relative to a crossbar, assuming

- Cost of a k x k switch grows quadraticaly with the number of unidirectional ports

- Cost of a 1 x k switch grows only linearly

Relative

$$cost_{switches} = \frac{2N(N-1)}{N^2} = 2(1 - \frac{1}{N})$$

Relative  $cost_{links} = \frac{N(N+1)}{2N} = \frac{N+1}{2}$

- As N increases, the switch cost nearly doubles the crossbar's

- Link cost is always higher than a crossbar's

- No extra benefits of a fully connected network over a crossbar!

### **Distributed Switched (Direct) Networks**

Example: Compute the switch and link costs of interconnecting N nodes using a fully connected topology relative to a crossbar

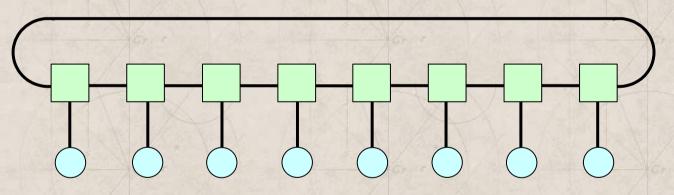

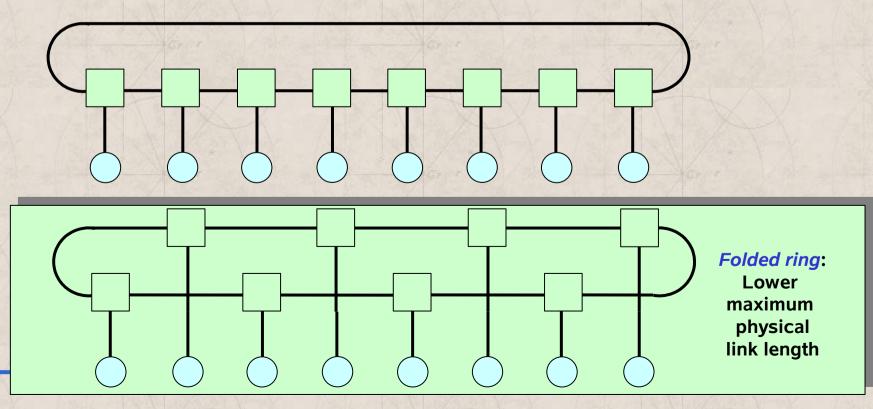

- Bidirectional Ring networks

- N switches  $(3 \times 3)$  and N bidirectional network links

- Simultaneous packet transport over disjoint paths

- Packets must hop across intermediate nodes

- Shortest direction usually selected (N/4 hops, on average)

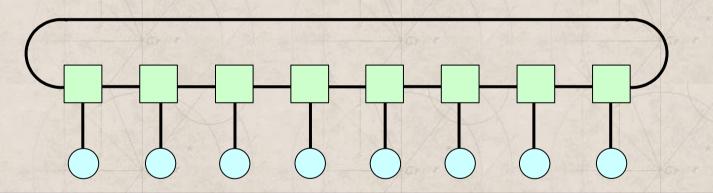

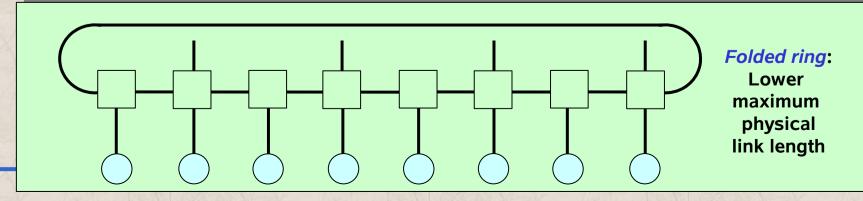

- Bidirectional Ring networks (folded)

- N switches  $(3 \times 3)$  and N bidirectional network links

- Simultaneous packet transport over disjoint paths

- Packets must hop across intermediate nodes

- Shortest direction usually selected (N/4 hops, on average)

- Bidirectional Ring networks (folded)

- N switches  $(3 \times 3)$  and N bidirectional network links

- Simultaneous packet transport over disjoint paths

- Packets must hop across intermediate nodes

- Shortest direction usually selected (N/4 hops, on average)

- Fully connected and ring topologies delimit the two extremes

- The ideal topology:

- Cost approaching a ring

- Performance approaching a fully connected (crossbar) topology

- More practical topologies:

- k-ary n-cubes (meshes, tori, hypercubes)

- > k nodes connected in each dimension, with n total dimensions

- > Symmetry and regularity

- » network implementation is simplified

- » routing is simplified

Duato

José

**Timothy Mark Pinkston and**

Interconnection Networks: ©

major presentation

Flich

ÓSÁ

from

contribution

#### **Distributed Switched (Direct) Networks**

with

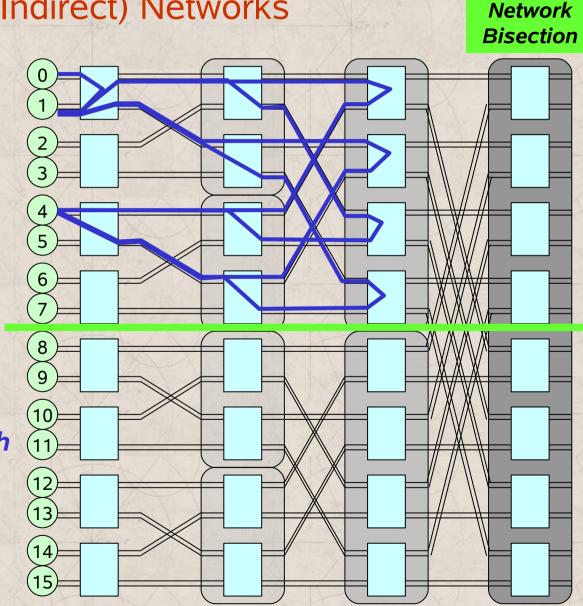

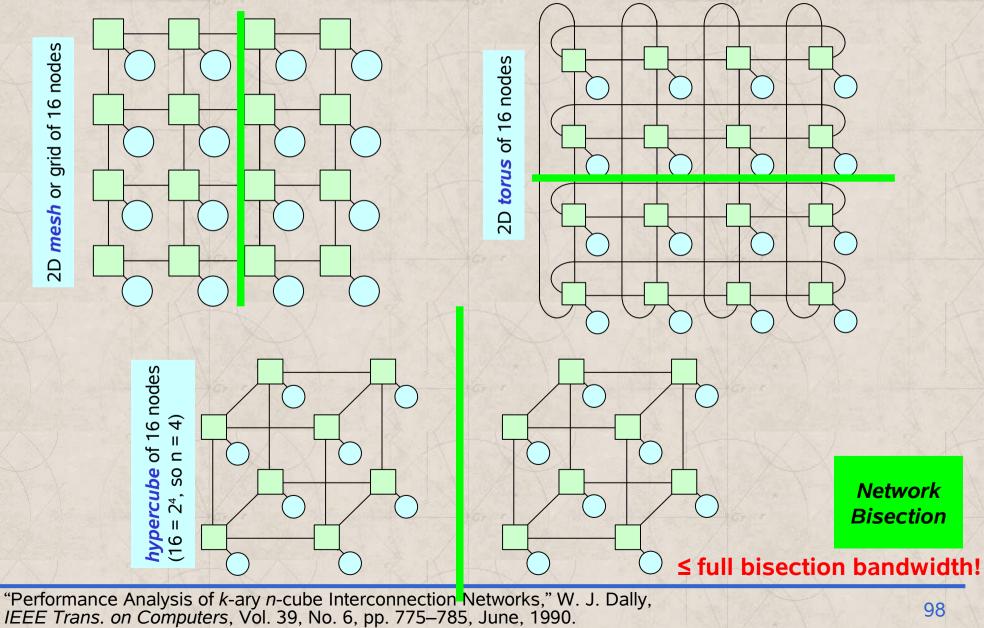

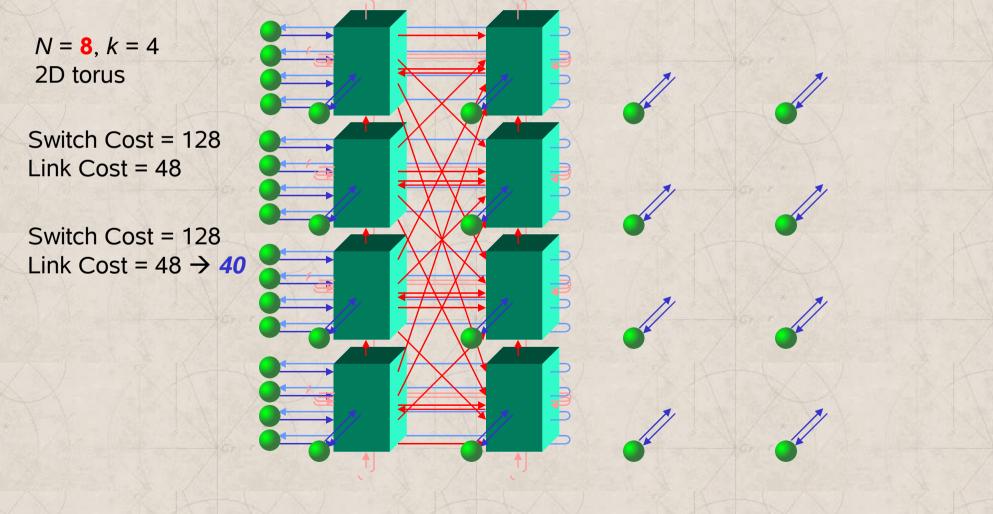

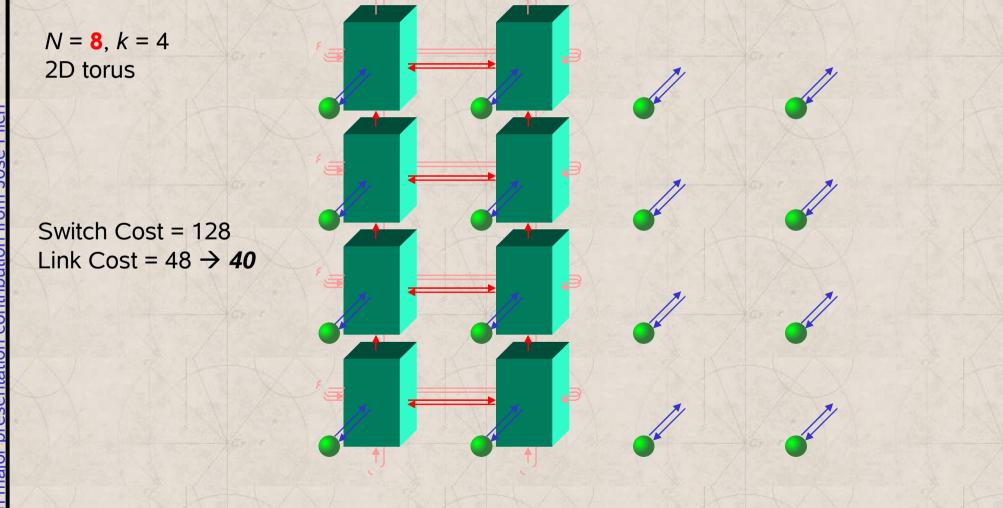

### **Comparison of Indirect and Direct Networks**

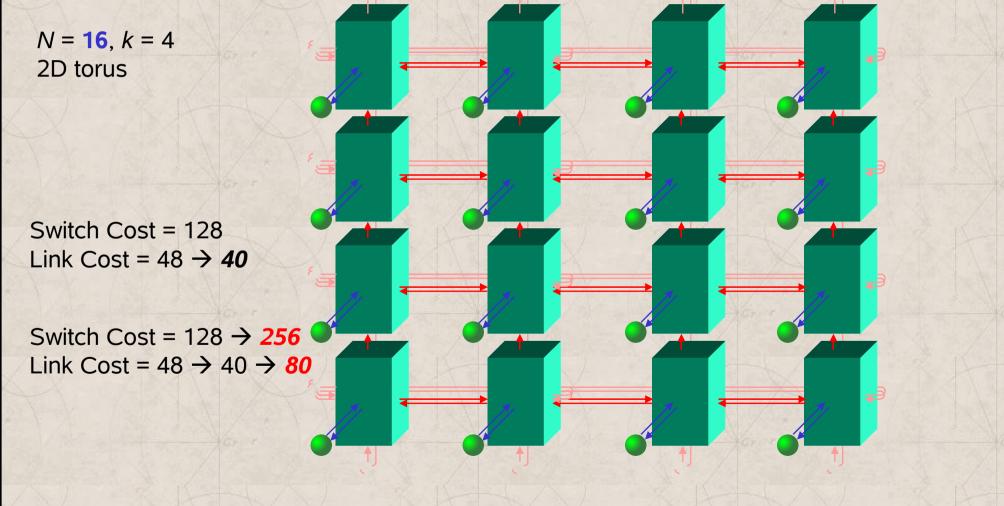

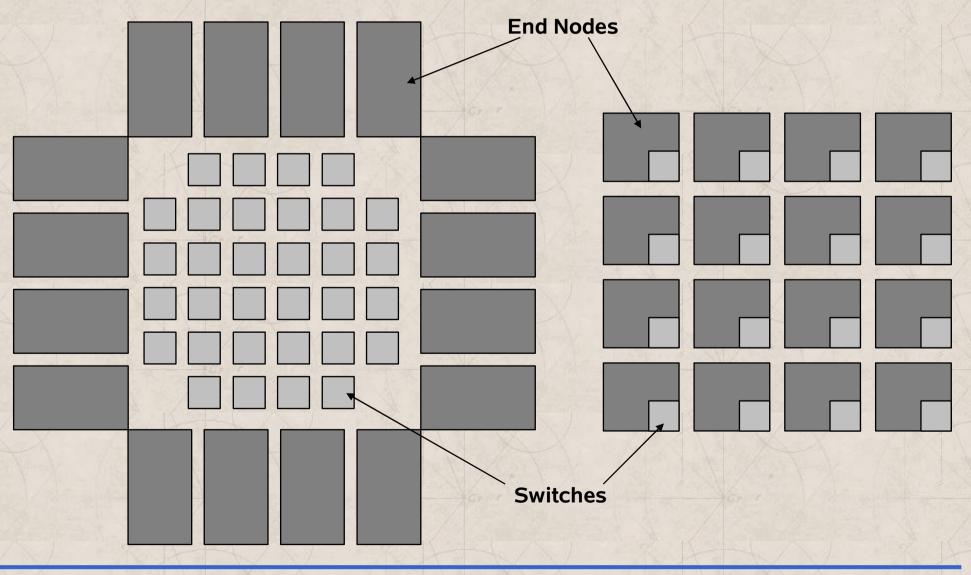

Indirect networks have end nodes connected at network periphery

*N* = 16, *k* = 4 fat tree-like MIN Switch Cost = 128 Link Cost = 48

### **Comparison of Indirect and Direct Networks**

Direct networks have end nodes connect in network area/volume

### **Comparison of Indirect and Direct Networks**

Direct networks have end nodes connect in network area/volume

#### **Comparison of Indirect and Direct Networks**

Direct networks have end nodes connect in network area/volume

### **Comparison of Indirect and Direct Networks**

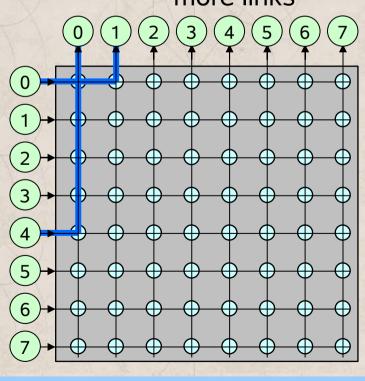

- Bristling can be used to reduce direct network switch & link costs

- "b" end nodes connect to each switch, where b is bristling factor

- Allows larger systems to be built from fewer switches and links

- Requires larger switch degree

- For N = 32 and k = 8, fewer switches and links than fat tree

64-node system with 8-port switches, **b** = 4

32-node system with 8-port switches

Duato

José

Timothy Mark Pinkston and

0

Interconnection Networks:

Flich

osé

from

contribution

sentation

pre

major

with

### **Comparison of Indirect and Direct Networks**

Distance scaling problems may be exacerbated in on-chip MINs

#### **Comparison of Indirect and Direct Networks**

Example: Compute the switch and link costs of interconnecting N nodes using a torus (<u>without bristling</u>) relative to a fat tree, assuming

$-k \ge k$  switches (fat tree), *n* dimensions (torus)  $2n+1 \ge k$

relative\_cost\_{switches} =

$$\frac{(2n+1)^2 N}{2kN\log_{k/2} N} = \frac{(2n+1)^2}{2k\log_{k/2} N} = \frac{k}{2\log_{k/2} N}$$

relative\_cost\_{links} =  $\frac{(n+1)N}{N\log_{k/2} N} = \frac{n+1}{\log_{k/2} N}$

- If switch degree (k) is low relative to N, tori have lower cost

- If switch degree (k) is high relative to N, fat trees have lower cost

- For N = 256 and k = 4, fat tree is four times more expensive!!

- For N = 256 and k = 8, fat tree is comparable in cost to torus (3D)

#### **Comparison of Indirect and Direct Networks**

Example: Compute the switch and link costs of interconnecting N nodes using a torus (<u>without bristling</u>) relative to using a fat tree

### **Comparison of Indirect and Direct Networks**

- Blocking reduced by maximizing dimensions (switch degree)

- Can increase bisection bandwidth, but

- Additional dimensions may increase wire length (must observe 3D packaging constraints)

- > Flow control issues (buffer size increases with link length)

- > Pin-out constraints (limit the number of dimensions achievable)

| V     | Evaluation category                | Bus   | Ring    | 2D mesh | 2D torus | Hypercube | Fat tree | Fully<br>connected |

|-------|------------------------------------|-------|---------|---------|----------|-----------|----------|--------------------|

| Perf. | BW <sub>Bisection</sub> in # links | 1     | 2       | 8       | 16       | 32        | 32       | 1024               |

|       | Max (ave.) hop count               | 1 (1) | 32 (16) | 14 (7)  | 8 (4)    | 6 (3)     | 11 (9)   | 1 (1)              |

| Cost  | I/O ports per switch               | NA    | 3       | 5       | 5        | 7         | 4        | 64                 |

|       | Number of switches                 | NA    | 64      | 64      | 64       | 64        | 192      | 64                 |

|       | Number of net. links               | 1     | 64      | 112     | 128      | 192       | 320      | 2016               |

|       | Total number of links              | 1     | 128     | 176     | 192      | 256       | 384      | 2080               |

Performance and cost of several network topologies for 64 nodes. Values are given in terms of bidirectional links & ports. Hop count includes a switch and its output link (in the above, end node links are not counted for the bus topology).

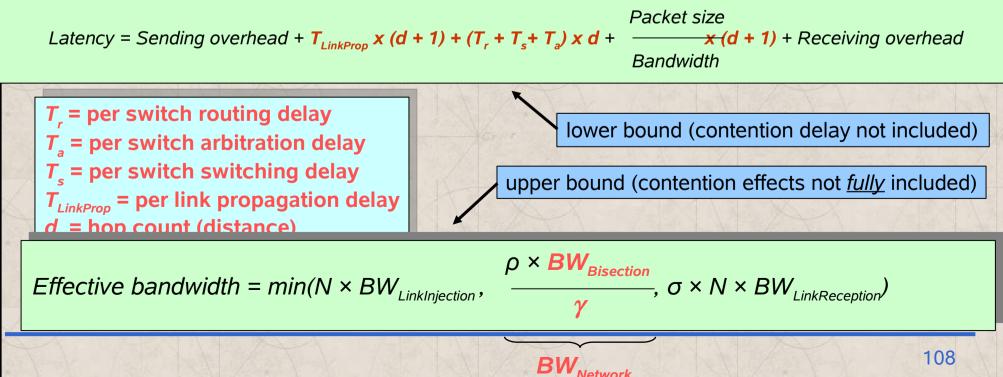

### **Characterizing Performance: Latency & Effective Bandwidth**

- Topology affects the number of hops, d, experienced by packets

- Transport functions (propagation, routing, switching, arbitration, and transmission) are performed on each hop through switches

- Topology affects  $BW_{Bisection}$ ; affects  $\gamma$  only for bus & dedicated-link

- Network traffic pattern determines  $\gamma$

### **Network Topology**

### Characterizing Performance: Latency & Effective Bandwidth

### **Network Topology**

### Characterizing Performance: Latency & Effective Bandwidth

# **Network Topology**

### **Topological Characteristics of Commercial Machines**

| No 150   | Company       | System<br>[Network] Name                   | Max.<br>number<br>of nodes<br>[x # CPUs] | Basic network topology                                        | Injection<br>[Recept'n]<br>node BW<br>in<br>MBytes/s | # of data<br>bits per<br>link per<br>direction | Raw<br>network link<br>BW per<br>direction in<br>Mbytes/sec | Raw<br>network<br>bisection<br>BW (bidir)<br>in Gbytes/s |

|----------|---------------|--------------------------------------------|------------------------------------------|---------------------------------------------------------------|------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|

|          | Intel         | ASCI Red<br>Paragon                        | 4,510<br>[x 2]                           | 2-D mesh<br>64 x 64                                           | 400<br>[400]                                         | 16 bits                                        | 400                                                         | 51.2                                                     |

| 200      | ІВМ           | ASCI White<br>SP Power3<br>[Colony]        | 512<br>[x 16]                            | BMIN w/8-port bidirect.<br>switches (fat-tree or<br>Omega)    | 500<br>[500]                                         | 8 bits (+1<br>bit of<br>control)               | 500                                                         | 256                                                      |

|          | Intel         | Thunter Itanium2<br>Tiger4<br>[QsNet"]     | 1,024<br>[x 4]                           | fat tree w/8-port<br>bidirectional<br>switches                | 928<br>[928]                                         | 8 bits (+2<br>control for<br>4b/5b enc)        | 1,333                                                       | 1,365                                                    |

| No.      | Cray          | XT3<br>[SeaStar]                           | 30,508<br>[x 1]                          | 3-D torus<br>40 x 32 x 24                                     | 3,200<br>[3,200]                                     | 12 bits                                        | 3,800                                                       | 5,836.8                                                  |

| 15 100   | Cray          | X1E                                        | 1,024<br>[x 1]                           | 4-way bristled<br>2-D torus (~ 23 x 11)<br>with express links | 1,600<br>[1,600]                                     | 16 bits                                        | 1,600                                                       | 51.2                                                     |

| 2        | ІВМ           | ASC Purple<br>pSeries 575<br>[Federation]  | >1,280<br>[x 8]                          | BMIN w/8-port<br>bidirect. switches<br>(fat-tree or Omega)    | 2,000<br>[2,000]                                     | 8 bits (+2<br>bits of<br>control)              | 2,000                                                       | 2,560                                                    |

| 1. 1. 1. | ІВМ           | Blue Gene/L<br>eServer Sol.<br>[Torus Net] | 65,536<br>[x 2]                          | 3-D torus<br>32 x 32 x 64                                     | 612,5<br>[1,050]                                     | 1 bit (bit<br>serial)                          | 175                                                         | 358.4                                                    |

| 1        | Martin Street | Star Star Star                             | No.                                      | Service States                                                | the and the state                                    |                                                | No. 2 - States                                              | - No. 17.2                                               |

# Outline

- E.1 Introduction (Lecture 1)

- E.2 Interconnecting Two Devices (Lecture 1)

- E.3 Interconnecting Many Devices (Lecture 2)

- E.4 Network Topology (Lecture 2)

- E.5 Network Routing, Arbitration, and Switching (Lecture 3)

- Routing

- Arbitration

- Switching

- Characterizing Performance: Latency & Effective Bandwidth

- E.6 Switch Microarchitecture (Lecture 4)

- E.7 Practical Issues for Commercial Interconnection Networks (Lec 4)

- E.8 Examples of Interconnection Networks (Lecture 5)

- E.9 Internetworking (skipped)

- E.10 Crosscutting Issues for Interconnection Networks (skipped)

- E.11 Fallacies and Pitfalls (Lecture 5)

- E.12 Concluding Remarks and References (Lecture 5)

### Routing

- Performed at each switch, regardless of topology

- Defines the "allowed" path(s) for each packet (Which paths?)

- Needed to <u>direct packets through network</u> to intended destinations

- Ideally:

- Supply as many routing options to packets as there are paths provided by the topology, and evenly distribute network traffic among network links using those paths, minimizing contention

- Problems: situations that cause packets never to reach their dest.

Livelock

- Arises from an unbounded number of allowed non-minimal hops

- > Solution: restrict the number of non-minimal (mis)hops allowed

- Deadlock

- Arises from a set of packets being blocked waiting only for network resources (i.e., links, buffers) held by other packets in the set

- > Probability increases with increased traffic & decreased availability

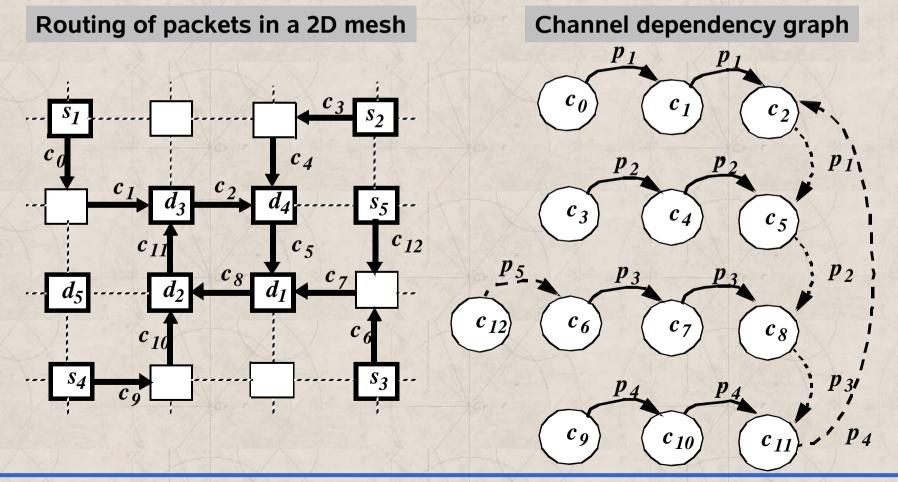

#### Routing

- Common forms of deadlock:

- Routing-induced deadlock

c<sub>i</sub> = channel i

s<sub>i</sub> = source node i

d<sub>i</sub> = destination node i

p<sub>i</sub> = packet i

"A Formal Model of Message Blocking and Deadlock Resolution in Interconnection Networks," S. Warnakulasuriya and T. Pinkston, *IEEE Trans. on Parallel and Distributed Systems*, Vol. 11, No. 3, pp. 212–229, March, 2000.

#### Routing

Common forms of deadlock:

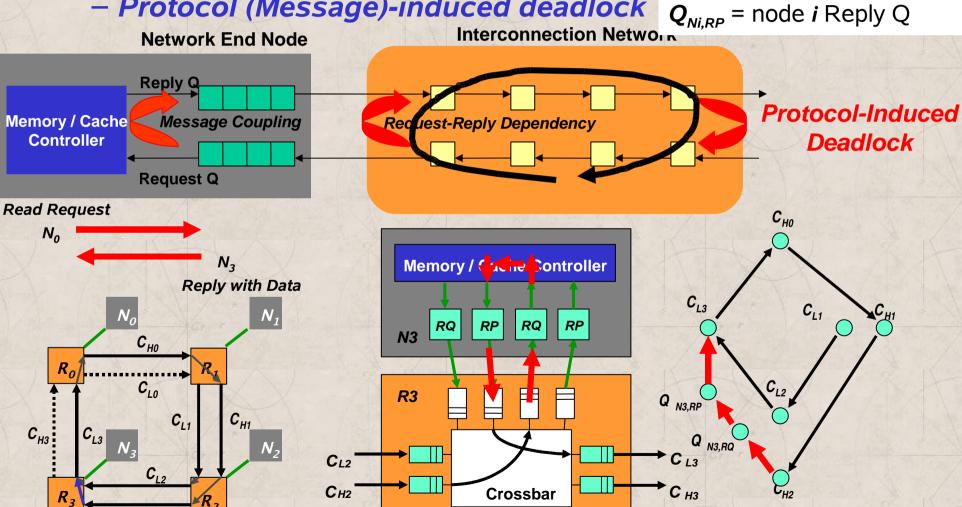

### Protocol (Message)-induced deadlock

C<sub>Hi</sub> = high-ordered channel *i*

$C_{Li}$  = low-ordered channel i

$Q_{Ni,RQ}$  = node *i* Request Q

"A Progressive Approach to Handling Message-Dependent Deadlocks in Parallel Computer Systems," Y. Song 15 and T. Pinkston, IEEE Trans. on Parallel and Distributed Systems, Vol. 14, No. 3, pp. 259–275, March, 2003.

#### Routing

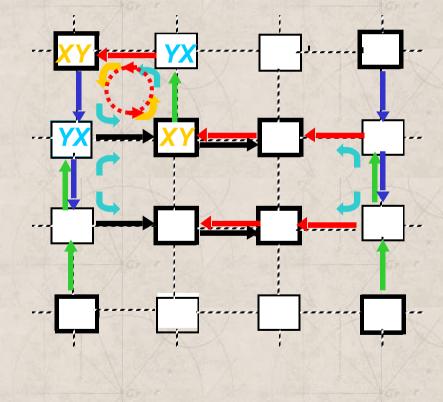

- Common forms of deadlock:

- Fault (Reconfiguration)-induced deadlock

• The transition from one routing function (**YX** routing) to another routing function (**XY** routing) in order to circumvent faults can create cyclic dependencies on resources that are not present in either routing function alone!

"Part I: A Theory for Deadlock-free Dynamic Reconfiguration of Interconnection Networks," J. Duato, O. Lysne<sub>116</sub> R. Pang, and T. Pinkston, *IEEE Trans. on Parallel and Distributed Systems*, Vol. 16, No. 5, pp. 412–427, May, 2005.

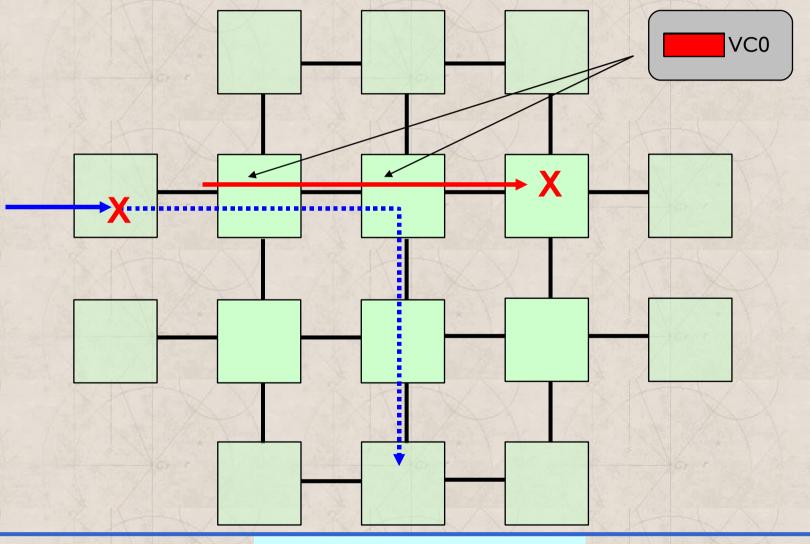

### Routing

- Common strategies to deal with all forms of deadlock

- Deadlock avoidance: restrict allowed paths only to those that keep the global state deadlock-free

- > *Duato's Protocol*: always guarantee an *escape path* from deadlock

- » Establish ordering only on a minimal (escape) set of resources

- » Grant escape resources in a partial or total order

- » Cyclic dependencies cannot form on escape resources, although cycles may form on larger set of network resources

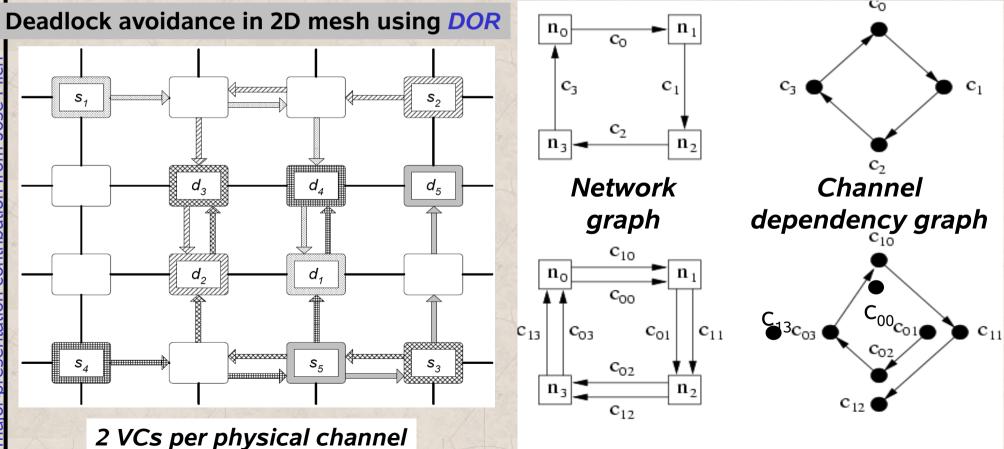

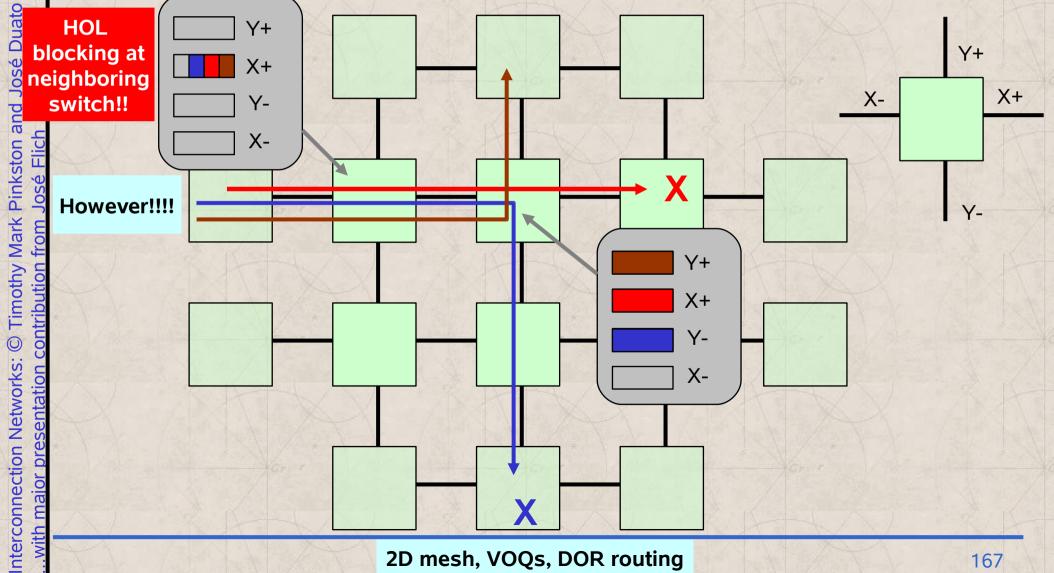

- > DOR (dimension-order routing) on meshes and hypercubes

- » Establish ordering on all resources based on network dimension

- > DOR on rings and tori (k-ary n-cubes with wrap-around links)

- » Ordering on all resources between and within each dimension

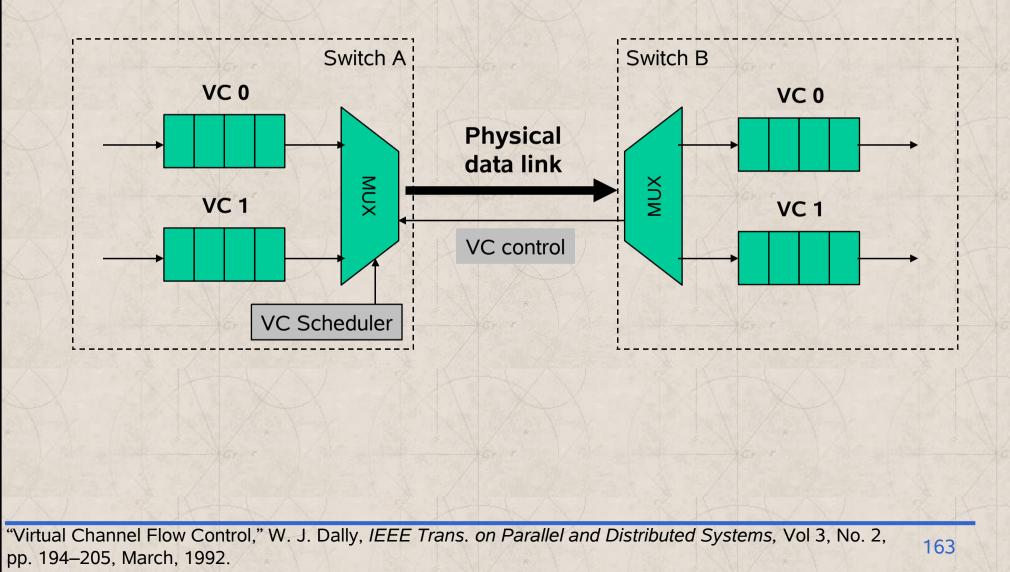

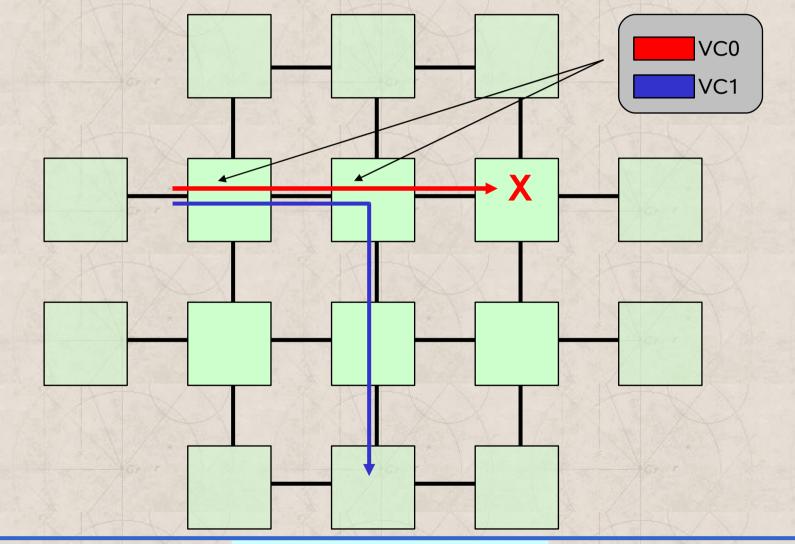

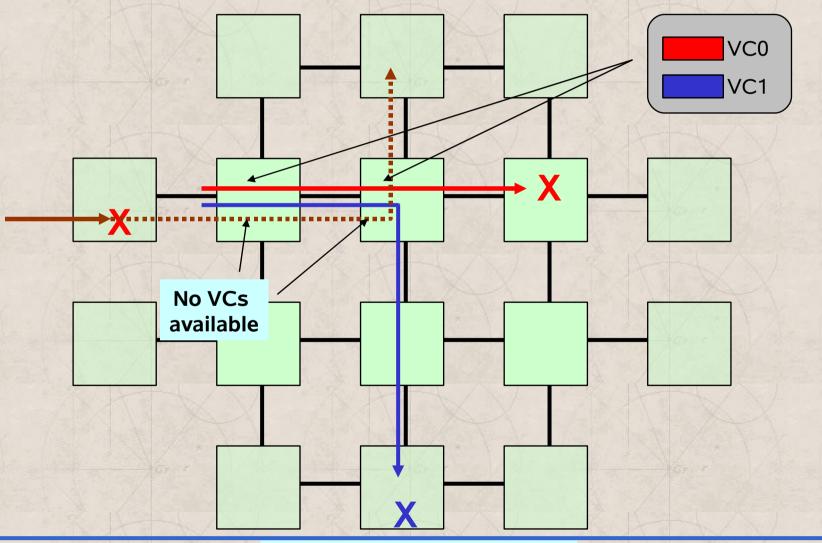

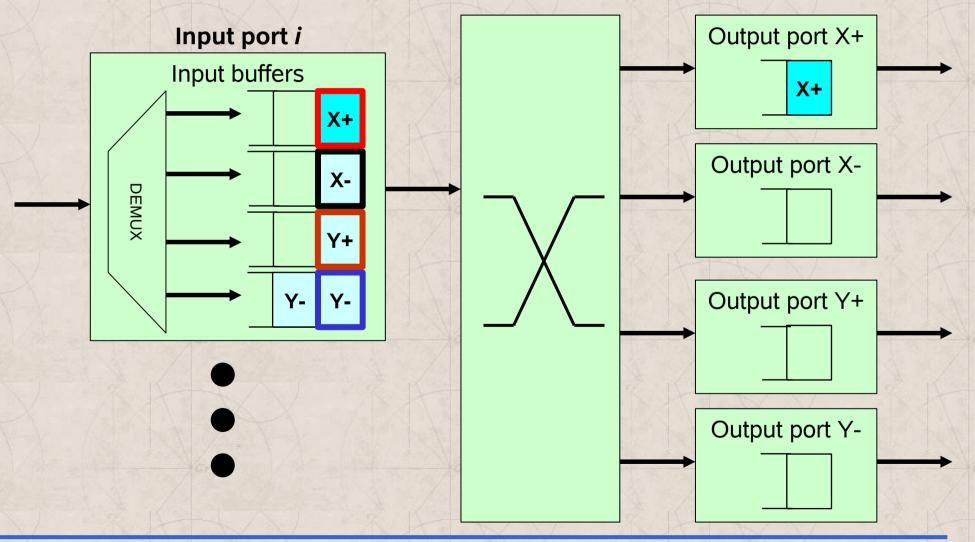

- » Apply to multiple virtual channels (VCs) per physical channel

- » Alternatively, keep resources along each dimension from reaching full capacity by ensuring the existence of a *bubble(s)*

#### Routing

- Common strategies to deal with deadlock

- Deadlock avoidance:

**n**<sub>i</sub> = node **i**

Deadlock avoidance in ring using VCs

- $c_i$  = physical channel i

- $c_{1i}$  = high-ordered VC i

**c**<sub>oi</sub> = low-ordered VC **i**

"A General Theory for Deadlock-free Adaptive Routing Using a Mixed Set of Resources," J. Duato and T. Pinkston, *IEEE Trans. on Parallel and Distributed Systems*, Vol. 12, No. 12, pp. 1219–1235, December, 2001.

### Routing

- Common strategies to deal with all forms of deadlock

- Deadlock recovery: allow deadlock to occur, but once a potential deadlock situation is detected, break at least one of the cyclic dependencies to gracefully recover

- > A mechanism to detect potential deadlock is needed

- Regressive recovery (abort-and-retry): remove packet(s) from a dependency cycle by killing (aborting) and later re-injecting (retry) the packet(s) into the network after some delay

- Progressive recovery (preemptive): remove packet(s) from a dependency cycle by rerouting the packet(s) onto a deadlockfree lane

- *Deterministic routing*: routing function always supplies the same path for a given source-destination pair (e.g., *DOR*)

- Adaptive routing: routing function allows alternative paths for a given source-destination pair (e.g., Duato's Protocol, Bubble Adaptive Routing, Disha Routing)

- Increases routing freedom to improve network efficiency, p

#### Routing

Duato

José Flich

Interconnection Networks: © Timothy Mark Pinkston and José

with major presentation contribution from

### Routing

- Routing in centralized switched (indirect) networks

- Least common ancestor (LCA) routing

- > Applicable to fat tree and other bidirectional MINs

- > Use resources in some partial order to avoid cycles, deadlock

- > Reach any LCA switch through any one of multiple paths

- > Traverse down the tree to destination through a deterministic path

- Self routing property: switch output port at each hop is given by shifts of the destination node address (least significant bit/digit)

#### – Up\*/down\* routing:

- > Universally applicable to any topology: map a tree graph onto it

- Assign "up" and "down" directions to network links (or VCs)

- Allowed paths to destination consist of zero or more "up" traversals followed by zero or more "down" traversals

- > Up-down traversals impose partial order to avoid cycles, deadlocks

#### Routing

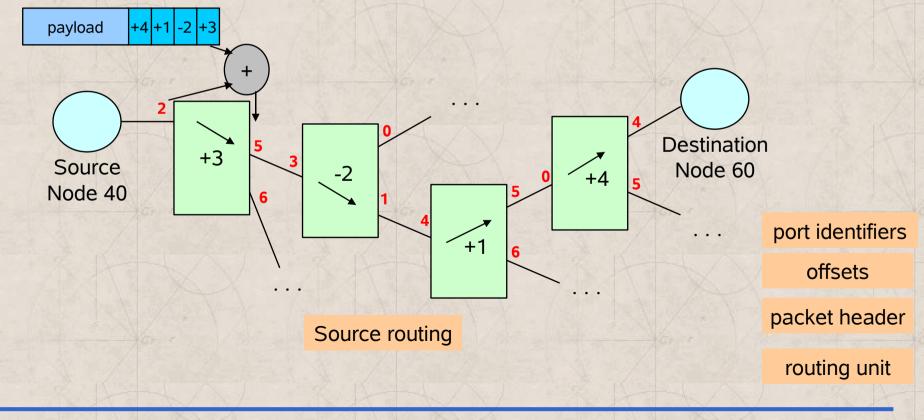

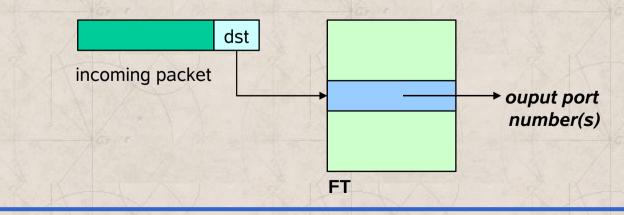

- Implementing the routing: source routing vs distributed routing

- Source routing (offset-based or could use absolute output port #)

- > Routing control unit in switches is simplified; computed at source

- > Headers containing the route tend to be larger  $\rightarrow$  increase overhead

### Routing

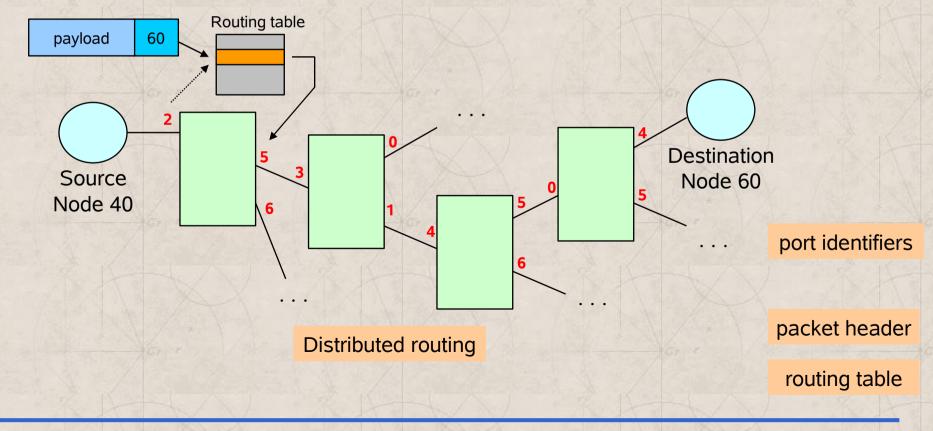

- Implementing the routing: source routing vs distributed routing

- Distributed routing

- > Next route computed by *finite-state machine* or by *table look-up*

- > Look-ahead routing is possible: the route one hop away is supplied

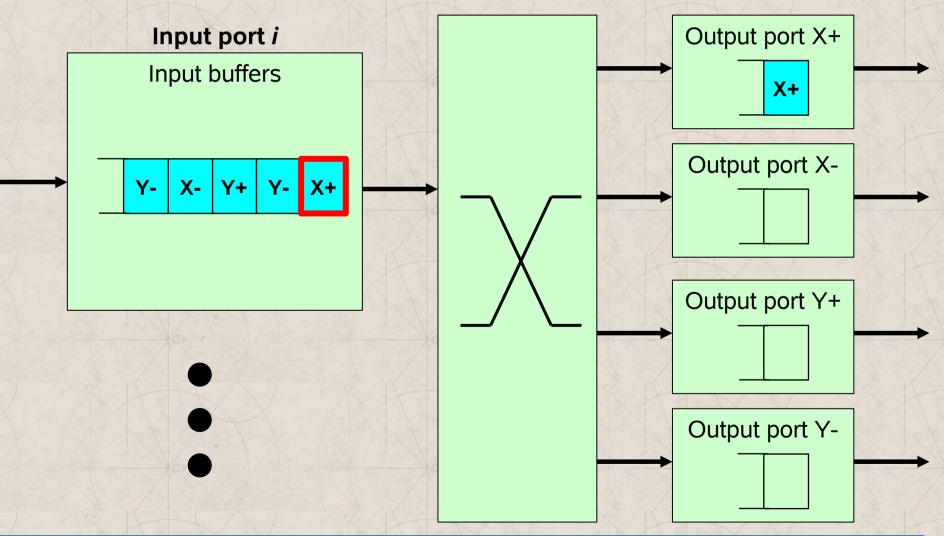

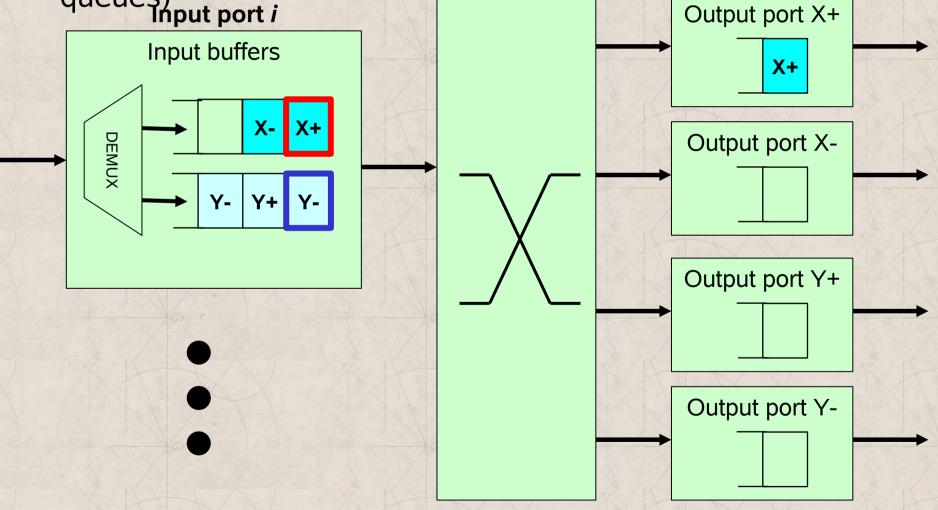

#### Arbitration

- Performed at each switch, regardless of topology

- Determines use of paths supplied to packets (When allocated?)

- Needed to <u>resolve conflicts for shared resources</u> by requestors

- Ideally:

- Maximize the matching between available network resources and packets requesting them

- At the switch level, arbiters maximize the matching of free switch output ports and packets located at switch input ports

- Problems:

- Starvation

- > Arises when packets can never gain access to requested resources

- > Solution: Grant resources to packets with fairness, even if prioritized

- Many straightforward distributed arbitration techniques for switches

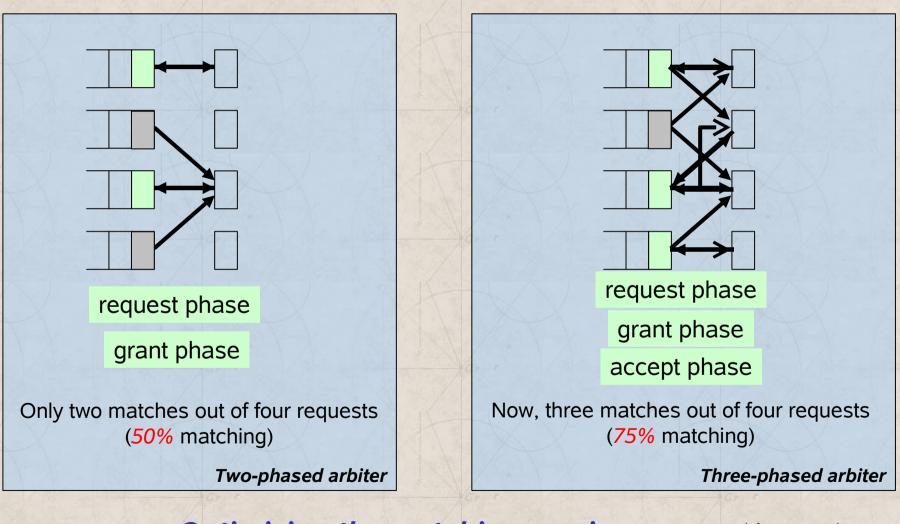

Two-phased arbiters, three-phased arbiters, and iterative arbiters

Arbitration

Duato

José

Timothy Mark Pinkston and

Interconnection Networks: © major presentation

with

Flich

losé

from

contribution

Optimizing the matching can increase  $\rho$  (i.e.,  $\rho_A$ )

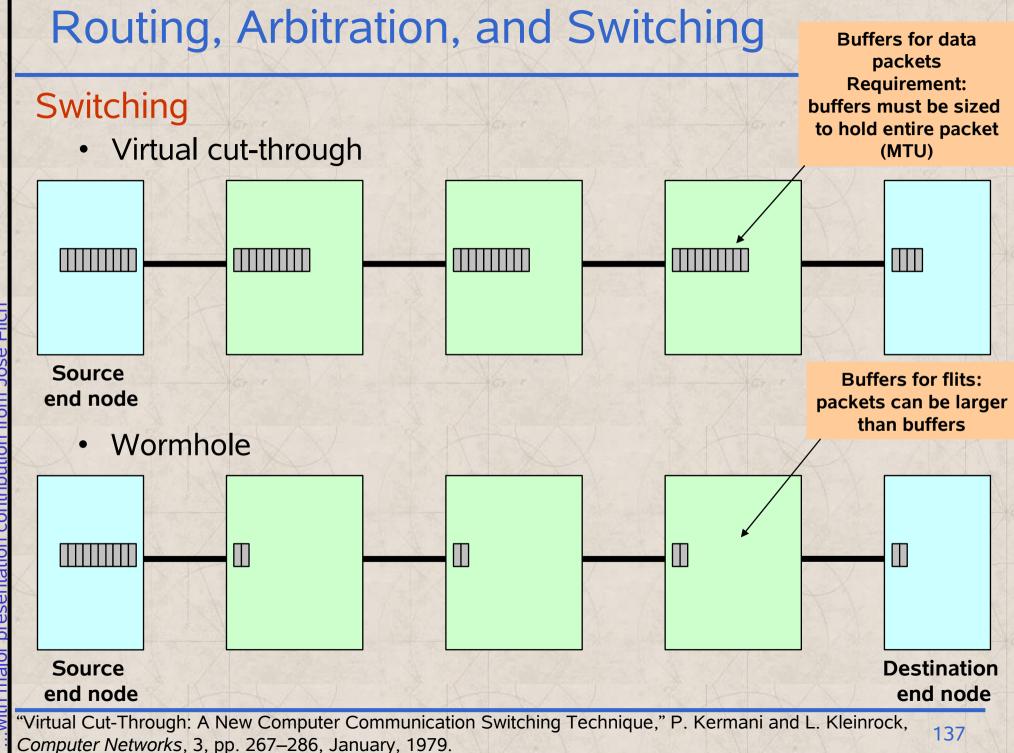

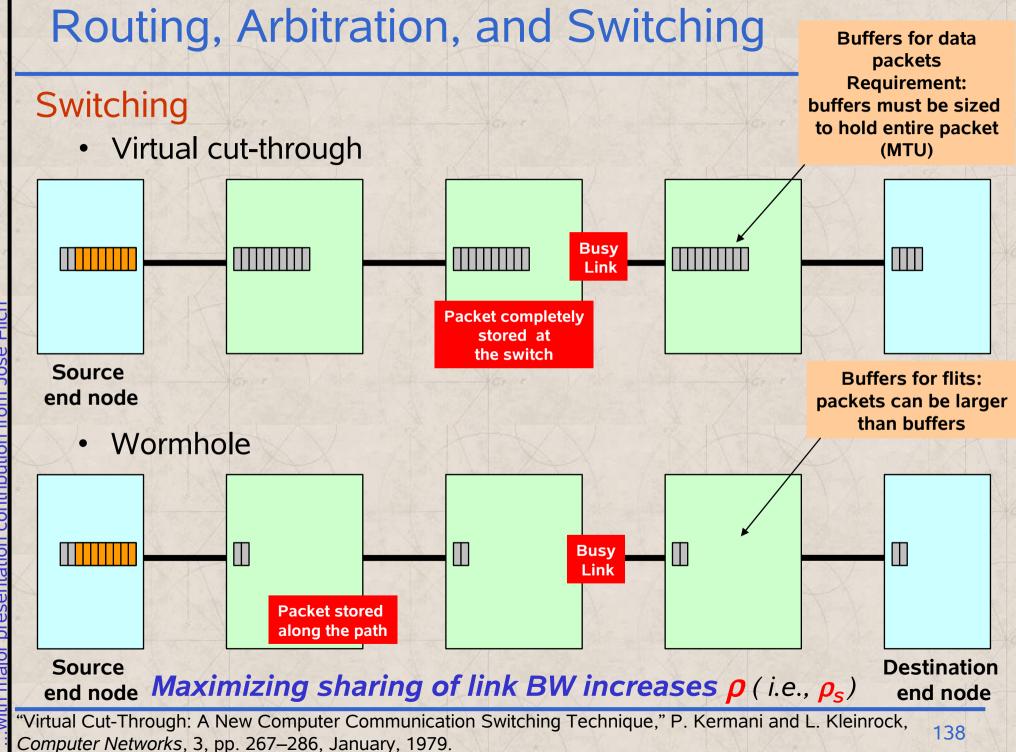

### Switching

- Performed at each switch, regardless of topology

- Establishes the connection of paths for packets (How allocated?)

- Needed to <u>increase utilization of shared resources</u> in the network

- Ideally:

- Establish or "switch in" connections between network resources (1) only for as long as paths are needed and (2) exactly at the point in time they are ready and needed to be used by packets

- Allows for efficient use of network bandwidth to competing flows

- Switching techniques:

- Circuit switching

- > pipelined circuit switching

- Packet switching

- Store-and-forward switching

- > Cut-through switching: virtual cut-through and wormhole

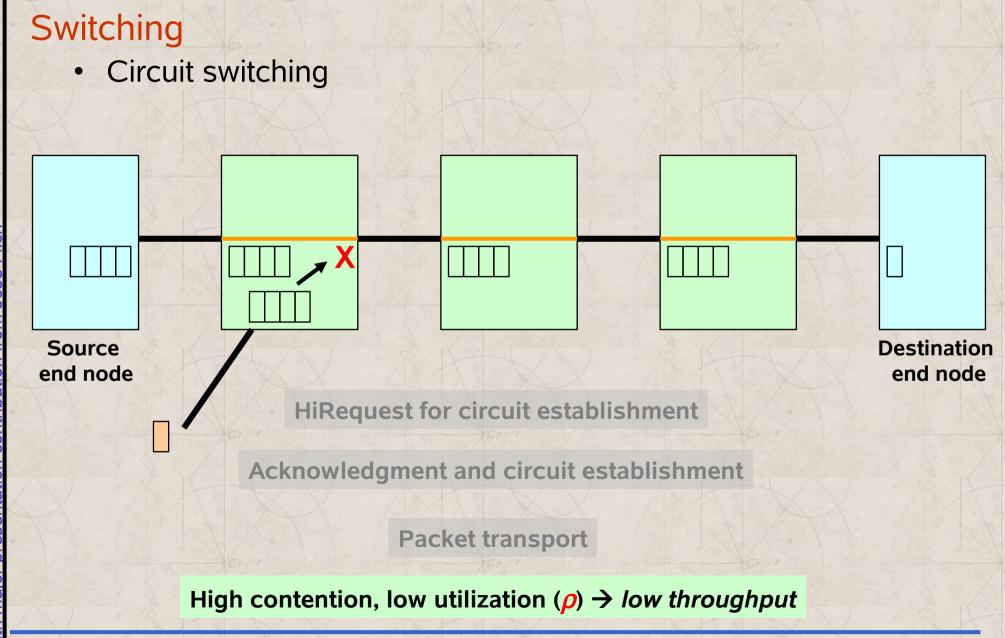

### Switching

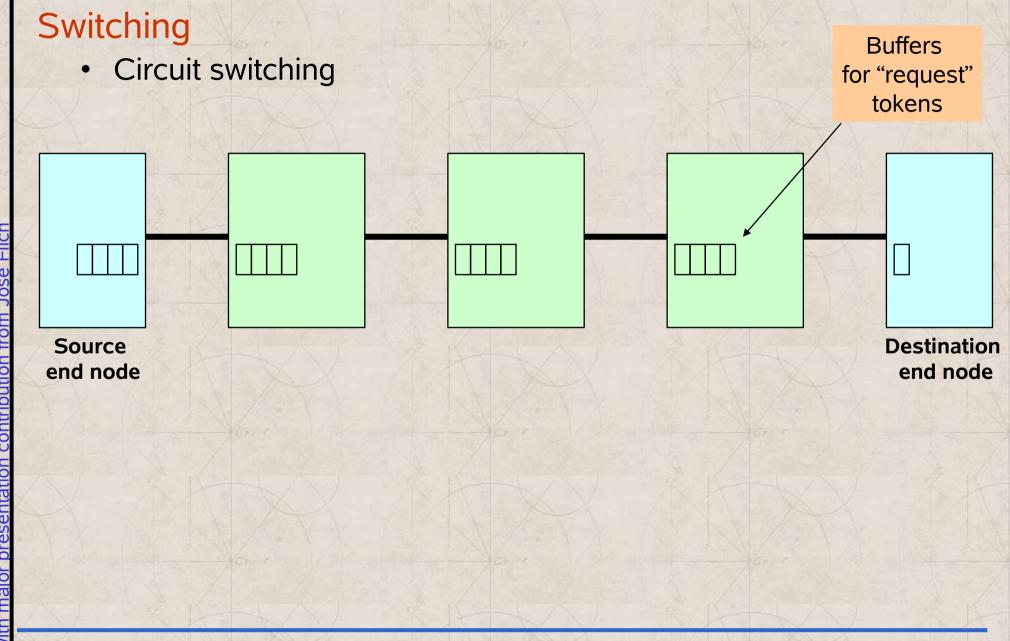

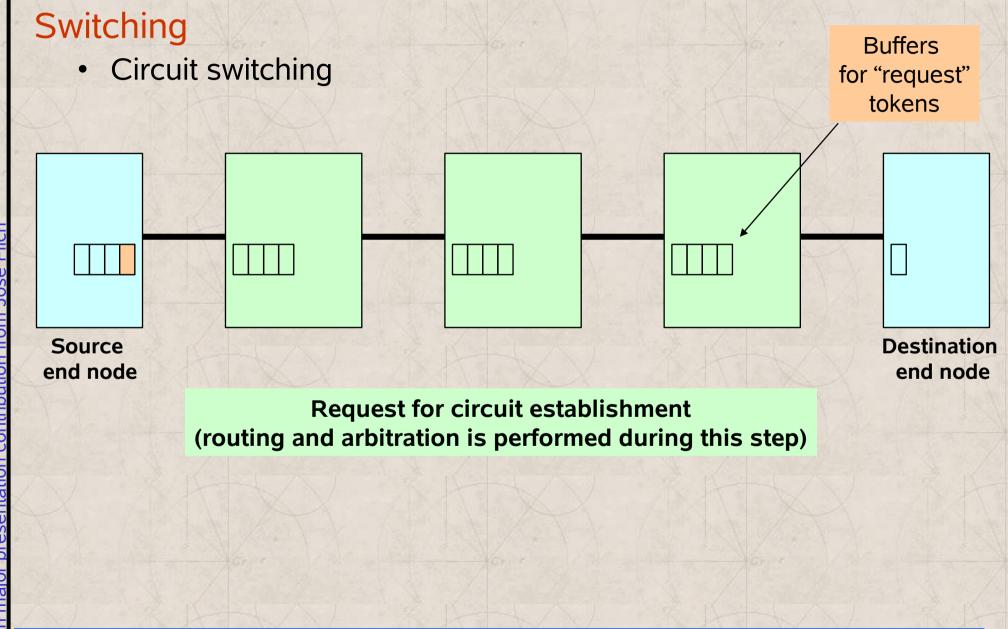

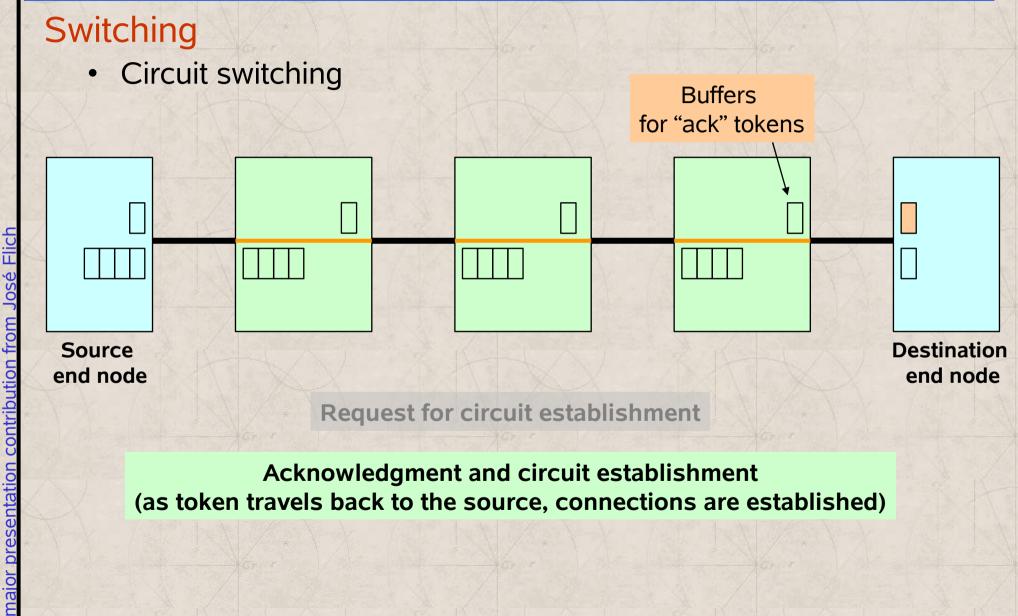

- Circuit switching

- A "circuit" path is established a priori and torn down after use

- Possible to pipeline the establishment of the circuit with the transmission of multiple successive packets along the circuit

> pipelined circuit switching

- Routing, arbitration, switching performed once for train of packets

- > Routing bits not needed in each packet header

- > Reduces latency and overhead

- Can be highly wasteful of scarce network bandwidth

- Links and switches go under utilized

- » during path establishment and tear-down

- » if no train of packets follows circuit set-up

Timothy Mark Pinkston and Interconnection Networks: © with

Duato

José

Switching Circuit switching ۲ Destination Source end node end node **Request for circuit establishment** Acknowledgment and circuit establishment **Packet transport** (neither routing nor arbitration is required)

Duato José Timothy Mark Pinkston and José Flich from contribution Interconnection Networks: © major presentation with

### Switching

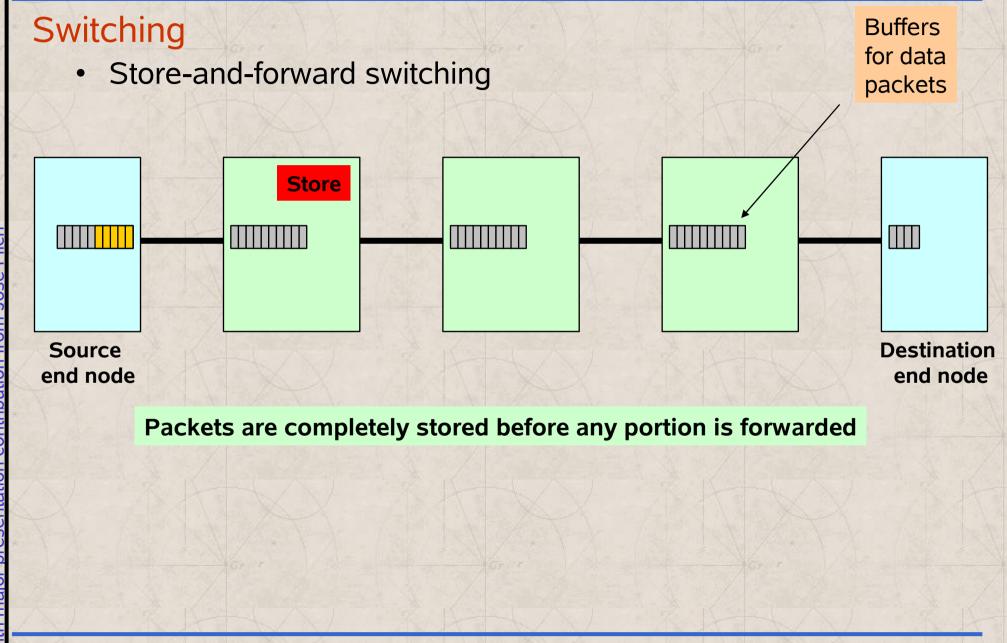

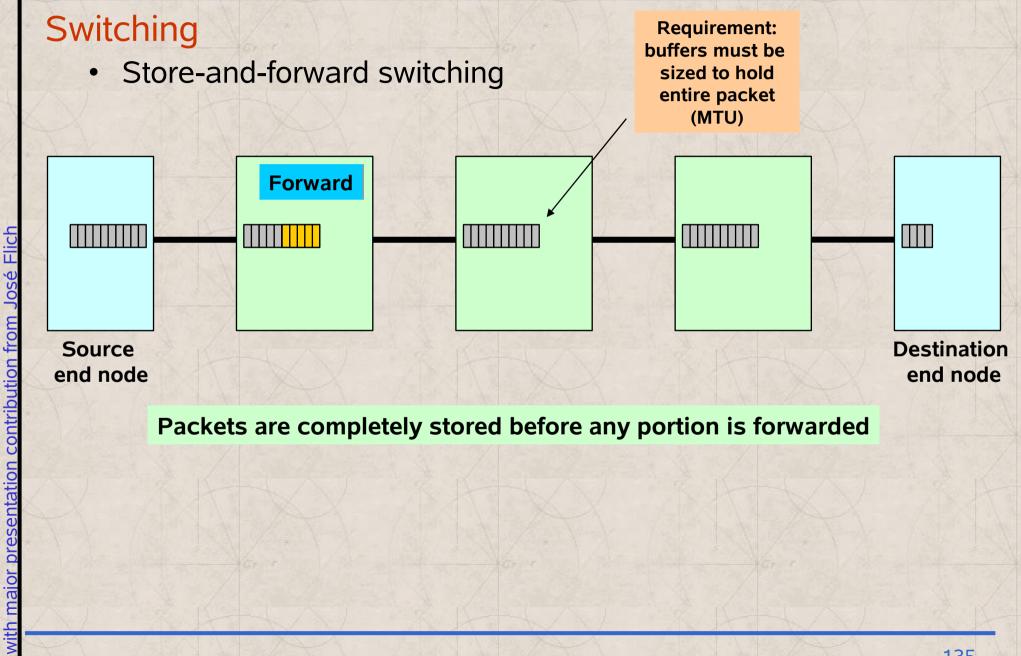

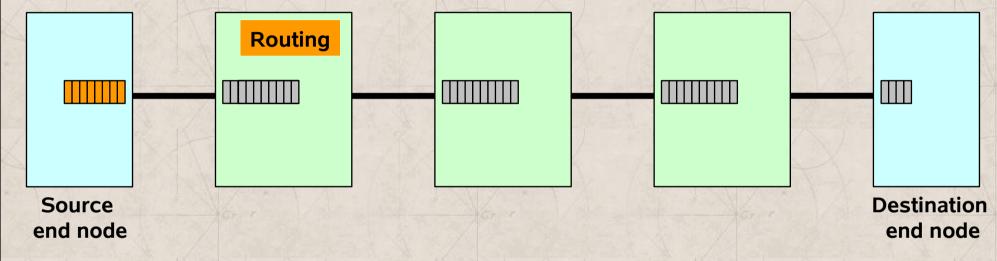

- Packet switching

- Routing, arbitration, switching is performed on a per-packet basis

- Sharing of network link bandwidth is done on a per-packet basis

- More efficient sharing and use of network bandwidth by multiple flows if transmission of packets by individual sources is more intermittent

- Store-and-forward switching

- > Bits of a packet are forwarded only after entire packet is first stored

- > Packet transmission delay is *multiplicative* with hop count, *d*

- Cut-through switching

- > Bits of a packet are forwarded once the header portion is received

- Packet transmission delay is <u>additive</u> with hop count, d

- Virtual cut-through: flow control is applied at the packet level

- *Wormhole*: flow control is applied at the flow unit (flit) level

- Buffered wormhole: flit-level flow control with centralized buffering

Duato

Duato

José

Timothy Mark Pinkston and

Interconnection Networks: ©

Switching

• Cut-through switching

Portions of a packet may be forwarded ("cut-through") to the next switch before the entire packet is stored at the current switch

Timothy Mark Pinkston and José Duato losé Flich from contribution Interconnection Networks: © sentation pre major

Timothy Mark Pinkston and José Duato losé Flich from contribution 0 Interconnection Networks: sentation pre major

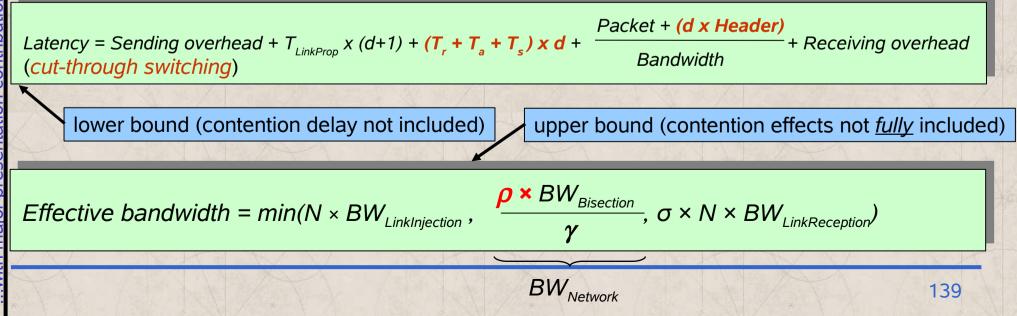

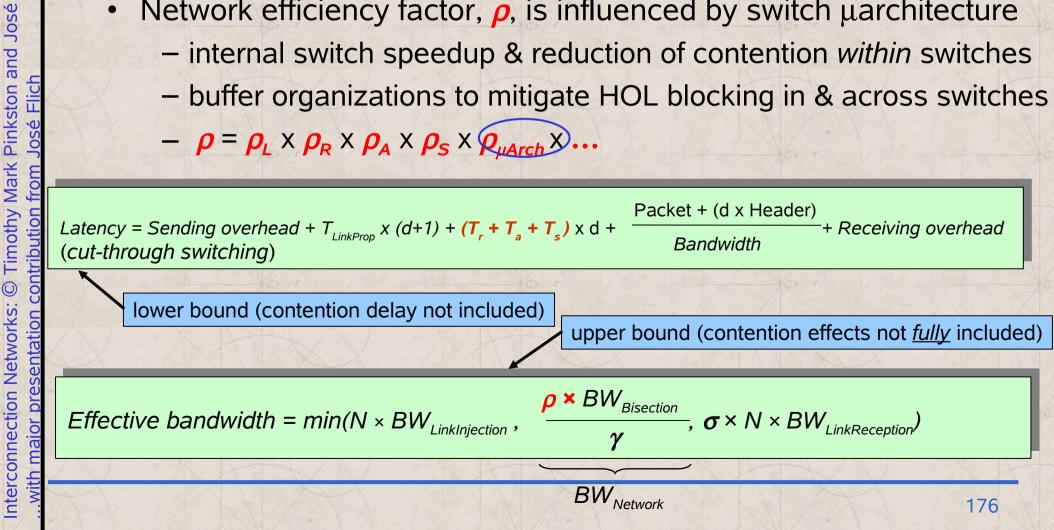

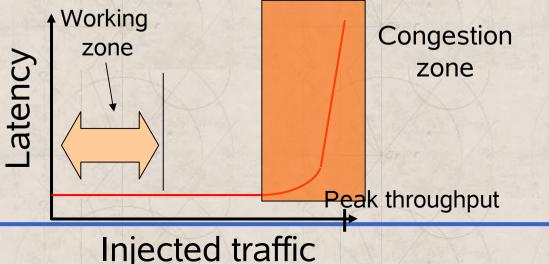

### Characterizing Performance: Latency & Effective Bandwidth

- At low network loads, routing and arbitration have little effect on performance as there is very little contention for shared resources

- Effective bandwidth affected by *network efficiency factor*,  $0 < \rho \leq 1$

- Routing can distribute traffic more evenly across bisection links

- Arbitration can maximize input-output matching, switch efficiency

- Switching can increase the degree of resource (link) sharing

$- \rho = \rho_L \times \rho_R \times \rho_A \times \rho_S \times \dots$

### Characterizing Performance: Latency & Effective Bandwidth

### Characterizing Performance: Latency & Effective Bandwidth

### Characterizing Performance: Latency & Effective Bandwidth

Characteristic performance plots: latency vs. average load rate; throughput (effective bandwidth) vs. average load rate

### Characterizing Performance: Latency & Effective Bandwidth

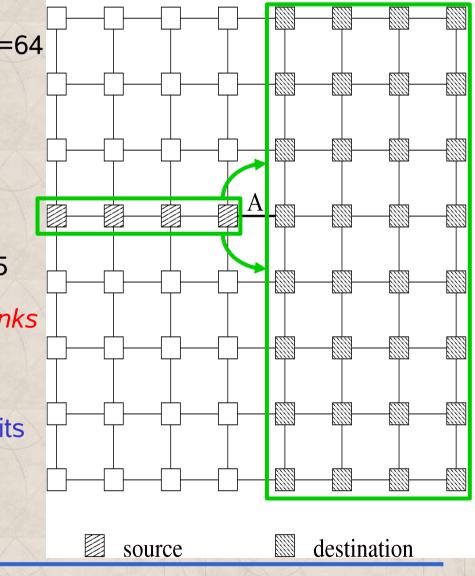

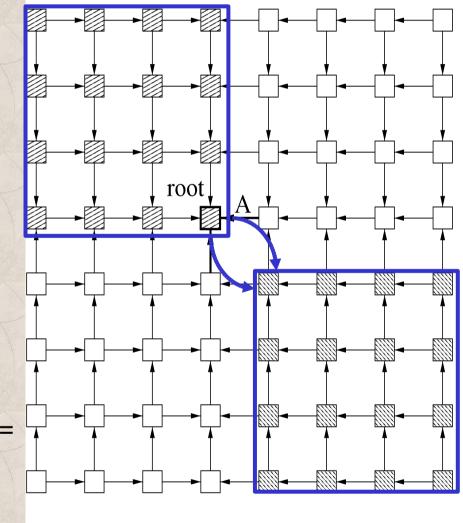

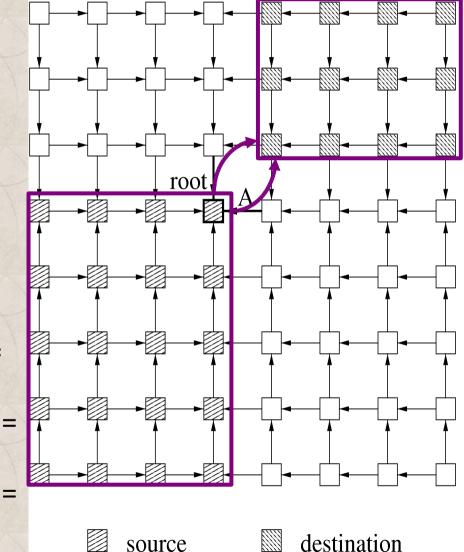

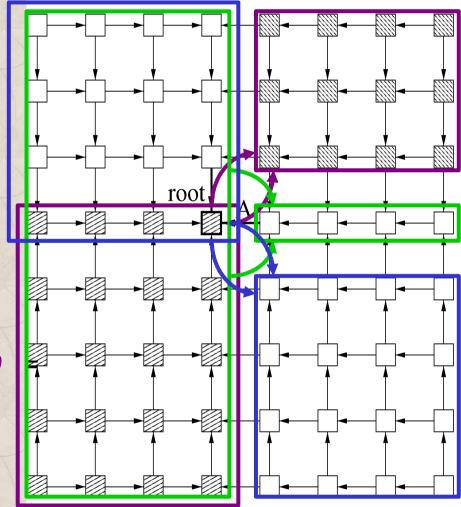

- Dimension-order routing on 2D mesh, N=64

- Uniformly distributed traffic

- $BW_{Bisection} = 2 \times 8 = 16$  link BW units

- $\forall \gamma = 2 \times (32 \times 32) / (64 \times 64) = 0.5$

- $BW_{Network}$  = 32 BW units, if  $\rho$  = 100%

- Fraction of overall traffic each link would carry is  $\gamma/Links_{Bisection} = 0.03125$

- DOR restrictions evenly load bisection links

- Link A carries (4 x 32)(64 x 64) =

0.03125 fraction of overall traffic

- Keeps *BW*<sub>Network</sub> at max of 32 BW units

- *p* = 32/32 = 100% (best case)

143

### Characterizing Performance: Latency & Effective Bandwidth

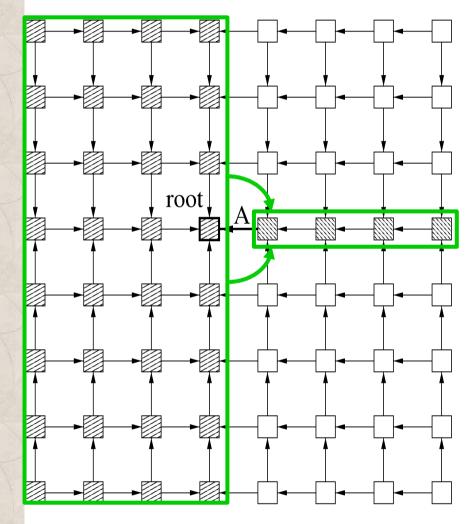

- Up\*/down\* routing on 2D mesh, N = 64

- Uniformly distributed traffic

- $BW_{Bisection} = 2 \times 8 = 16$  link BW units

- $\forall \gamma = 2 \times (32 \times 32) / (64 \times 64) = 0.5$

- $BW_{Network}$  = 32 BW units, if  $\rho$  = 100%

- fraction of overall traffic each link would carry is  $\gamma/Links_{Bisection} = 0.03125$

- U\*/D\* routing restrictions overload Link A

- Case 1: carries (32 x 4)/(64 x 64)

0.03125 fraction of overall traffic

source

Timothy Mark Pinkston and José Duato ontributio Networks: nterconnection

destination

### Characterizing Performance: Latency & Effective Bandwidth

=

- Up\*/down\* routing on 2D mesh, N = 64

- Uniformly distributed traffic

- $BW_{Bisection} = 2 \times 8 = 16$  link BW units

- $\forall \gamma = 2 \times (32 \times 32) / (64 \times 64) = 0.5$

- $BW_{Network}$  = 32 BW units, if  $\rho$  = 100%

- fraction of overall traffic each link would carry is  $\gamma/Links_{Bisection} = 0.03125$

- U\*/D\* routing restrictions overload Link A

- Case 1: carries (32 x 4)/(64 x 64)

0.03125 fraction of overall traffic

- Case 2: carries ½(16 x 16)/(64 x 64) = 0.03125 fraction of traffic

source

destination

145

Mark Pinkston and José Duato Timothy  $\bigcirc$ Networks: nterconnection

### Characterizing Performance: Latency & Effective Bandwidth

- Up\*/down\* routing on 2D mesh, N = 64

- Uniformly distributed traffic

- $BW_{Bisection} = 2 \times 8 = 16$  link BW units

- $\forall \gamma = 2 \times (32 \times 32) / (64 \times 64) = 0.5$

- $BW_{Network}$  = 32 BW units, if  $\rho$  = 100%

- fraction of overall traffic each link would carry is  $\gamma/Links_{Bisection} = 0.03125$

- U\*/D\* routing restrictions overload Link A

- Case 1: carries (32 x 4)/(64 x 64)

0.03125 fraction of overall traffic

- Case 2: carries ½(16 x 16)/(64 x 64) = 0.03125 fraction of traffic

- Case 3: carries ½(20 x 12)/(64 x 64) = 0.02930 fraction of traffic

### Characterizing Performance: Latency & Effective Bandwidth

- Up\*/down\* routing on 2D mesh, N = 64

- Uniformly distributed traffic

- $BW_{Bisection} = 2 \times 8 = 16$  link BW units

- $\forall \gamma = 2 \times (32 \times 32) / (64 \times 64) = 0.5$

- $BW_{Network}$  = 32 BW units, if  $\rho$  = 100%

- fraction of overall traffic each link would carry is  $\gamma/Links_{Bisection} = 0.03125$

- U\*/D\* routing restrictions overload Link A

- carries 0.03125 + 0.03125 + 0.02930 0.09180 fraction of overall traffic!!

- Limits BW<sub>Network</sub> to only <u>10.9 BW units</u>

- $\rho$  = 10.9 / 32 = <u>34%</u> (at most)

source

**Routing algorithm can impact** *ρ* **significantly!**

Duato José Mark Pinkston and Timothy Networks nterconnection

destination

Duato

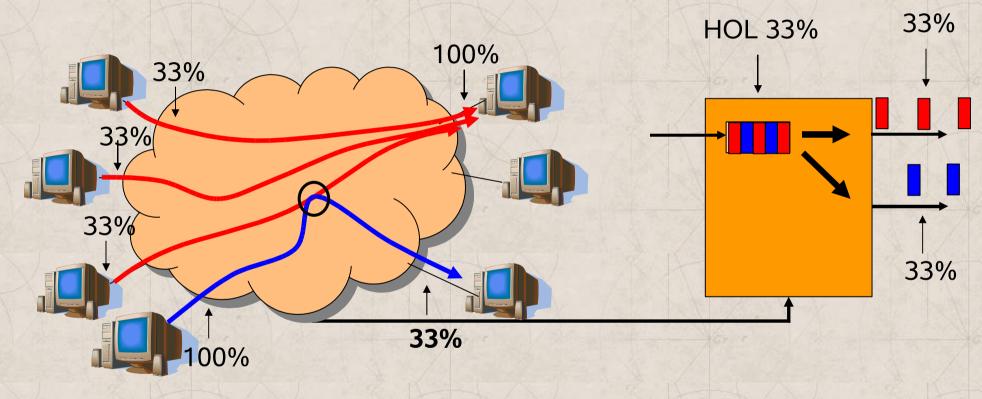

**Characterizing Performance: Latency & Effective Bandwidth**

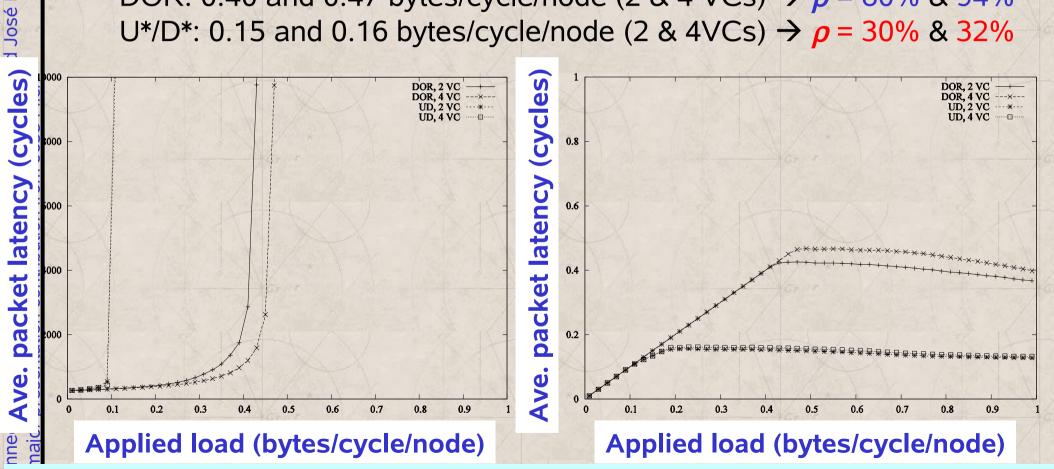

Measured p: DOR vs U\*/D\* on 2D Mesh, N = 64 (via simulation)

DOR: 0.40 and 0.47 bytes/cycle/node (2 & 4 VCs)  $\rightarrow \rho = 80\%$  & 94% U\*/D\*: 0.15 and 0.16 bytes/cycle/node (2 & 4VCs)  $\rightarrow \rho = 30\%$  & 32%

2D Mesh, N = 64 (8 x 8), virtual cut-through, 2 & 4 virtual channels (VCs), uniform traffic assumed. DOR vs. Up\*/Down\* routing used on all VCs. Ideal throughput is 0.5 bytes/cycle/node.

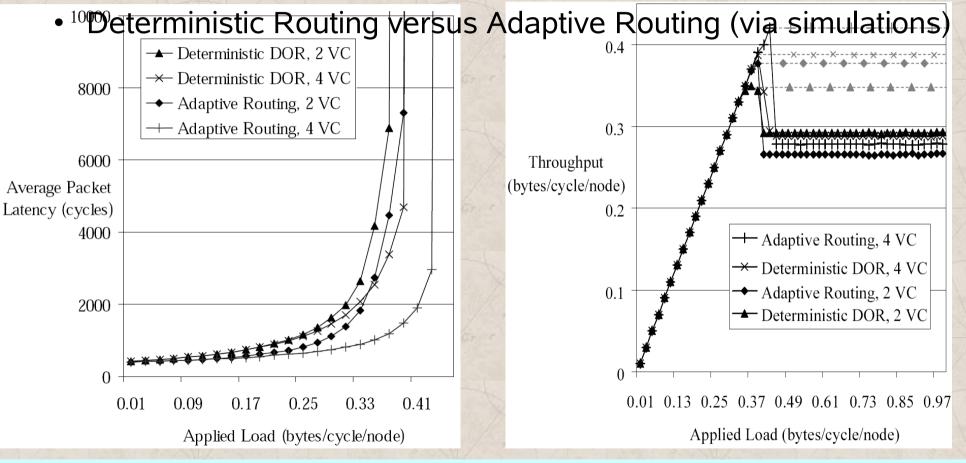

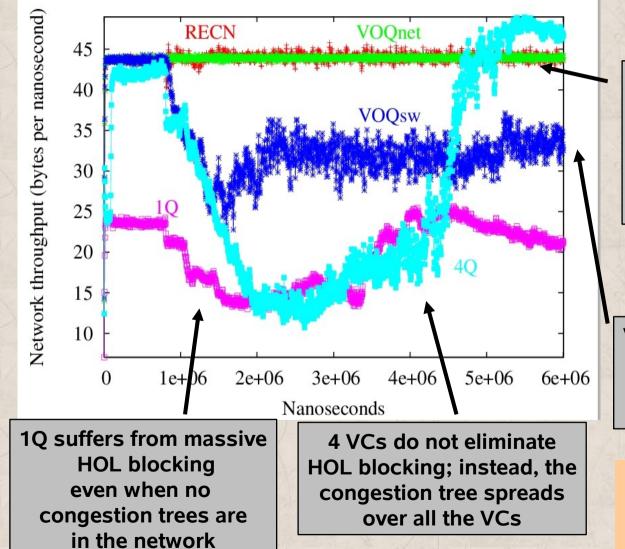

### Characterizing Performance: Latency & Effective Bandwidth

3-D Torus, 4,096 nodes (16 x 16 x 16), virtual cut-through switching, three-phase arbitration, 2 and 4 virtual channels. Bubble flow control in dimension order is used in one virtual channel; the other virtual channel is supplied in dimension order (*deterministic routing*) or along any shortest path to destination (*adaptive routing*). Uniform traffic is assumed.

### Characterizing Performance: Latency & Effective Bandwidth

- Efficiency factor ( $\rho$ ) for deterministic routing vs. adaptive routing

- Ideal (maximum) throughput: 0.5 bytes/cycle/node

- $\rightarrow \rho = 100\%$

- Enough injection and reception bandwidth (i.e., network bandwidth poses as the "pipe" bottleneck)

- > Bisection bandwidth (16x16x4 unidirectional links)

- » 1024 bytes/cycle bandwidth at the bisection

- » 0.25 bytes/cycle/node bandwidth at the bisection

- $\gamma = 0.5$

> Ideal throughput: 100% x ( $BW_{Bisection}$  /  $\gamma$ ) = 0.5 bytes/cycle/node

- Network efficiency,  $\rho$ , = measured throughput / ideal throughput

- > Adaptive routing with four VCs: p = 86%

- > Deterministic routing with two VCs:  $\rho = 74\%$

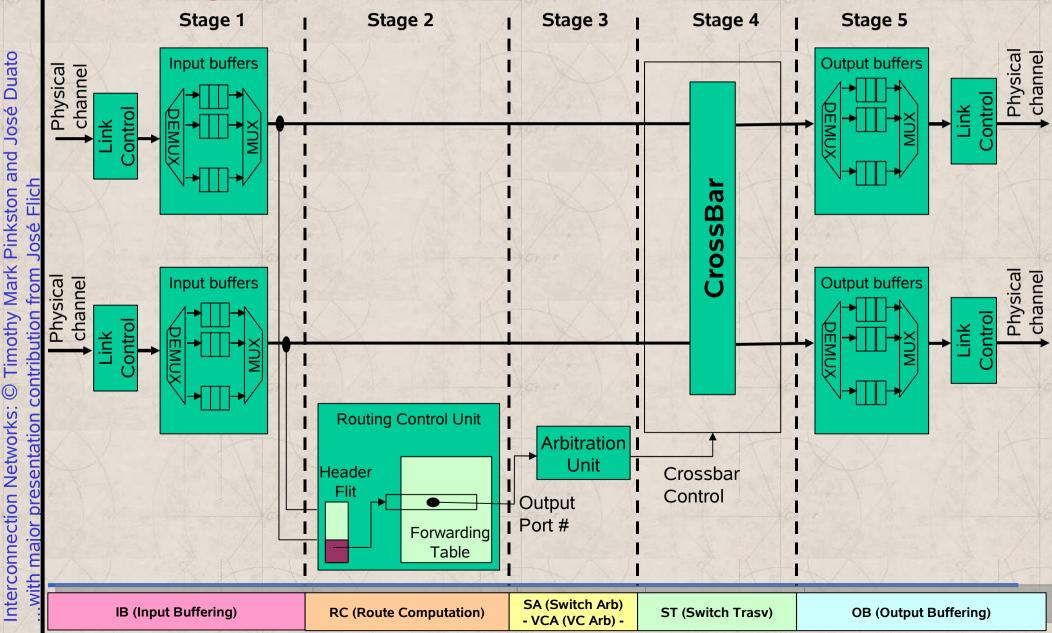

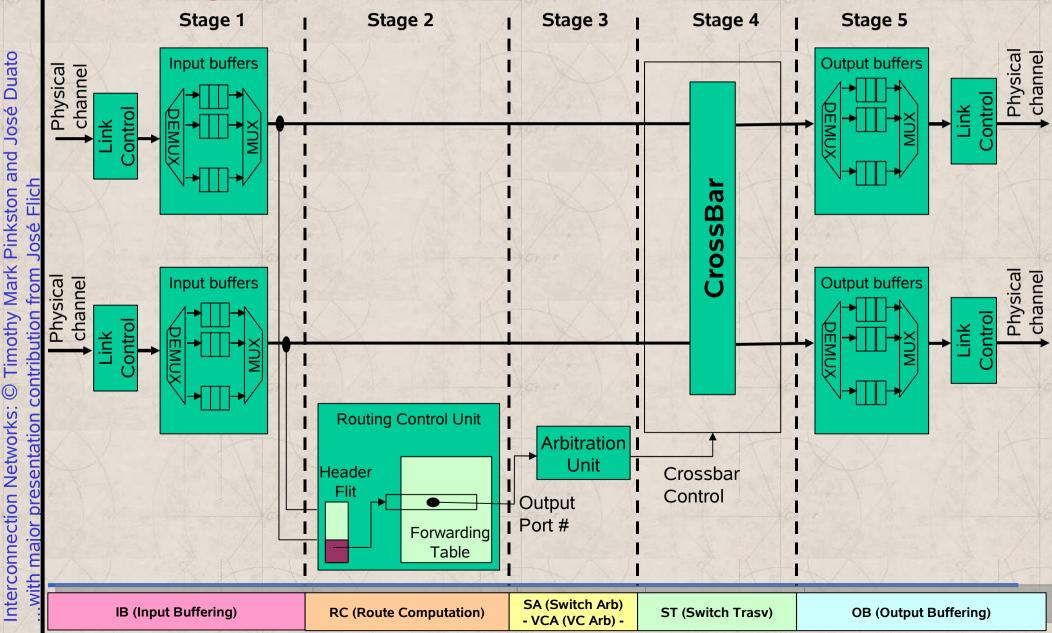

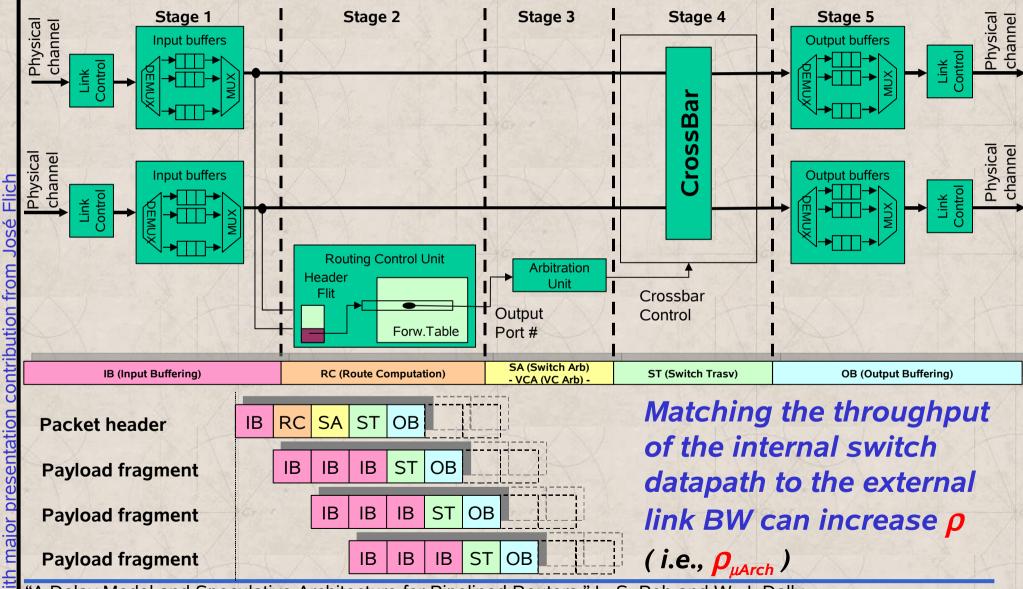

#### R, A, & S Characteristics of Commercial Machines

| Compan<br>y | System<br>[Network]<br>Name                | Max.<br>compute<br>nodes<br>[x #CPUs]                                                                                                                                                                                                         | Basic network<br>topology                                                                                                                                                                                                                                                                                                                                                                | Network routing<br>algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Switch<br>arbitration<br>scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Network<br>switching<br>technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

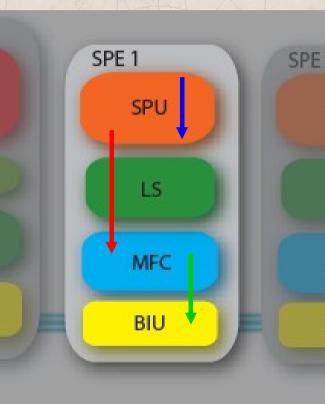

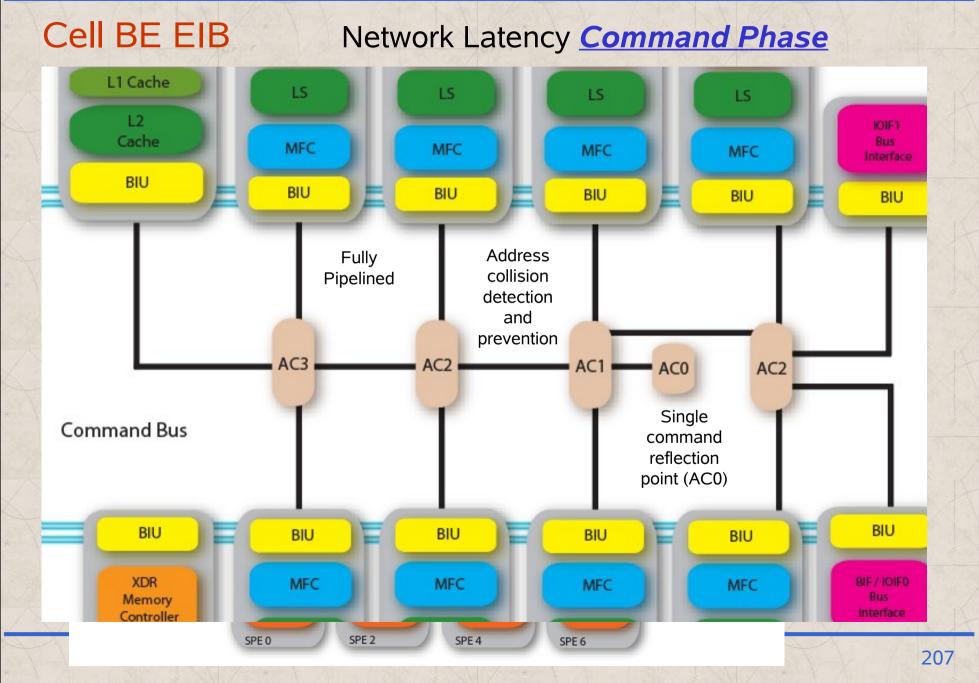

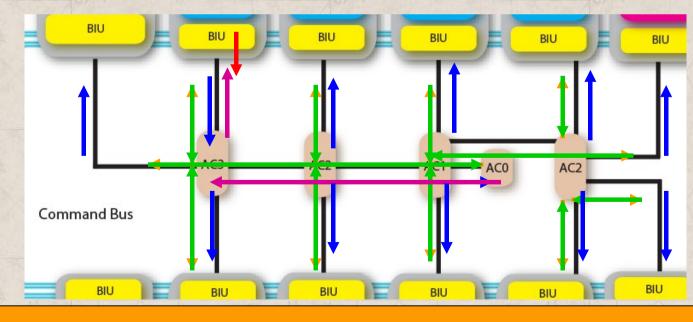

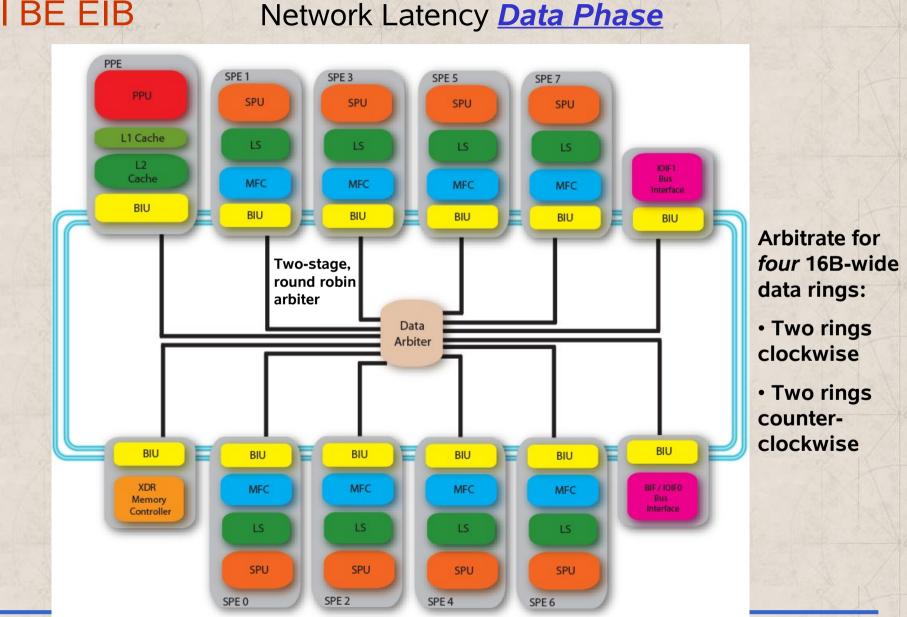

|-------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|